实现的方法还是比较简单的,对源时钟信号50MHZ进行计数即可,达到一定时间后输出翻转信号。

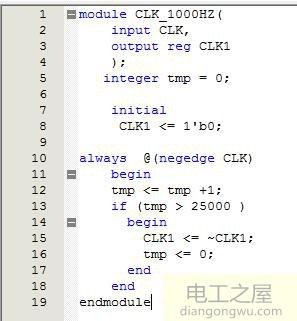

将50MHZ的时钟信号分频为1000HZ

50MHZ的时钟信号分频为1000HZ,50MHZ÷1000HZ=50000,即50000倍的关系,那么可将50MHZ的时钟信号进行计数,设置初始值CLK1=0,当计数达50000/2即25000次时,CLK1=~CLK1,即翻转,如此反复即可实现CLK1的输出信号为1000HZ。

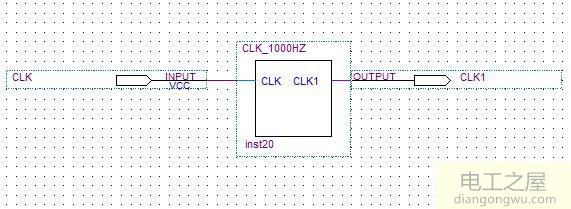

输出1000HZ时钟模块

输出1000HZ时钟Verilog程序

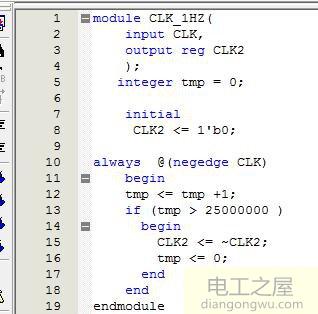

将50MHZ的时钟信号分频为1HZ

将50MHZ的时钟信号分频为1HZ,其实现原理差不多,50MHZ÷1HZ=50000000,那么可将50MHZ的时钟信号进行计数,设置初始值CLK2=0,当计数达50000000/2即25000000次时,CLK2=~CLK2,即翻转,如此反复即可实现CLK2的输出信号为1HZ。

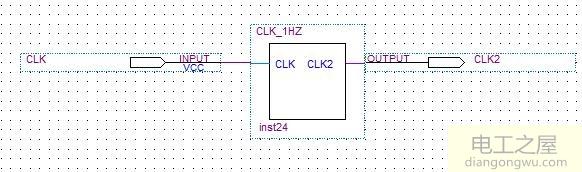

输出1HZ时钟模块

输出1HZ时钟Verilog程序