今天小编要和大家分享的是布线技巧与EMC相关信息,接下来我将从后端时序修正基本思路,02 4802这几个方面来介绍。

布线技巧与EMC相关技术文章后端时序修正基本思路

后端时序修正基本思路

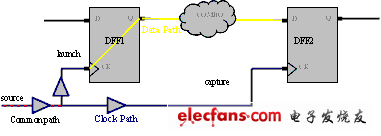

讲到时序优化的时候,就好比手工绘图讲到反相器一样,总会以上图为例介绍各种路径及时钟与彼此之间的关系。

后端对时序的影响从0.18开始,在整体影响中的比重也在随着工艺的变化而变得敏感。0.18似乎是一个分水岭,很多效应都在此后有了明显的变化。之所以讲到时比例,并不是说某种影响在一开始不存在或突然产生,这好比是量变到质变的过程。

要最终满足时序的要求,方方面面都要考虑。有时,单单靠后端无法达成要求,或者要付出更多的成本,比如面积或时间。这就需要流程中各个环节都要作出优化。

如图所示,红色为时钟共同路径,然后启动路径和捕获路径开始分开;黄色则是数据路径。当然,启动时钟与捕获时钟有时并非由同一时钟驱动,但分析方法是类似的。我们通常要解决建立时间与保持时间如何满足时序约束的问题。这就是说,数据到达DFF2的D端要提前在时钟到达DFF2的CK端一段时间前到达,又要在时钟后再保持一段时间后才能消失。那么我们要做的事是:

如果要满足建立时间时,希望

启动时钟延迟 + 数据延迟 < 捕获时钟延迟 [最慢]

如果要满足保持时间时,希望

启动时钟延迟 + 数据延迟 > 捕获时钟延迟 [最快]

那么,这里可以变化的范围就是一个时钟周期,也就是,如果时钟到达两个寄存器时钟端的时间一致, 数据路径能变化的范围就是一个时钟周期。

延迟中,时钟延迟称为clock latency, 数据延迟称为delay,时钟延迟有时钟源延迟与时钟网络延迟。路径延迟中的增与减的项大致如下:

延迟增加:clock network delay, clock uncertainty(hold), input external delay, time borrowed from endpoint

延迟减少:clock uncertainty(setup) , output external delay, library setup/hold time, clock gating setup/hold time

其他,如果设置derate也会因路径快慢影响路径的延迟。

如此,后端修改时序的基本思路(流程)就可以大致分开成几个步骤:

1,建立时序优化(减小数据路径延迟)

2,时钟树综合与平衡

3,保持时序优化(增加数据路径延迟)

这里,在时钟树满足要求后,通常不再对时钟路径进行修改,为了避免发生变化,通常要设置dont_touch_network。

IC compiler 中涉及的命令包括:place_opt, clock_opt, route_opt及psynopt

place_opt 意在摆放优化与保持时序优化,保持时序不进行优化。为了不让该命令进行时钟树综合与保持时序优化,就注意设定理想时钟,并去除fix_hold 属性。

clock_opt 进行时钟树的综合与优化,此时设定fix_hold 进行保持时序优化。

route_opt 进行布线与优化,减小耦合影响等

psynopt 可以进行单独时序优化。

当然,这些只是后端时序优化的基本思路,最关键的还是要正确设置,并且对设计的结构作出合理调整,并注意前后端在整个流程中发挥的作用与对成本的影响。

关于布线技巧与EMC就介绍完了,您有什么想法可以联系小编。