今天小编要和大家分享的是布线技巧与EMC相关信息,接下来我将从基于IBIS建模仿真的信号完整性问题解决方案,ibis 模型:信号完整性分析的一种渠道,第1 部分这几个方面来介绍。

布线技巧与EMC相关技术文章基于IBIS建模仿真的信号完整性问题解决方案

高速数字设计人员面临的一个挑战就是处理其电路板上的过冲、下冲、错配阻抗振铃、抖动分布和串扰问题。这些问题都可归入信号完整性范畴。许多高速设计人员都使用输入/输出缓冲信息规范 (IBIS) 建模语言来预见并解决信号完整性问题。该建模语言自 20 世纪 90 年代以来便得到广泛的运用,并已发展成为一种正式的标准:EIA-ANSI 656-B。IBIS 论坛2008 年 8 月发布的第 5 版标准仍然盛行。IBIS 使用电流-电压 (I-V) 和电压-时间 (V-t) 数据表来描述某个器件的 I/O 引脚特性。厂商们通过仿真或测量其器件 I/O 单元生成这些表。

对于那些现在高达 20 Gbits/秒时钟频率的高速设计来说,我能够理解对于这类系统仿真工具的需求。IBIS 使得 SPICE 仿真选项显得不那么重要,因为仿真时间大大缩短,并且拥有同样的准确度。我所说的 IBIS 仿真时间更短,是相对于一个大型 PCB 系统需要数天或数周时间来完成一次晶体管级 SPICE 仿真而言的,其执行一次 IBIS 仿真只需数分钟或几小时的时间。通过一次 IBIS 仿真,您可以生成许多传输线响应和眼图。

IBIS 格式已经表明了其在高速应用行业中的价值。然而,它让我真正感到吃惊的地方是广大客户现在正要求提供对更低频率器件(例如:低于 40 MHz 的时钟器件)的 IBIS 支持。最初,我以为组件工程师们一直试图标准化其校验表。现在,我并不那么确定了。即使在更低频率下,我们也面临许多信号完整性问题,这是因为数字信号边缘速率。这些快速边缘速率负责振铃的时钟信号,从而引起一条命令甚至 ADC 突发 2 增益的错译。IC 厂商拥有非常成熟的 SPICE 仿真宏模型,可用于精密器件,但是他们正紧跟我们的 IBIS 数字 I/O 模型库。图 1 描述了一个 IBIS 模型仿真非常有效的例子。

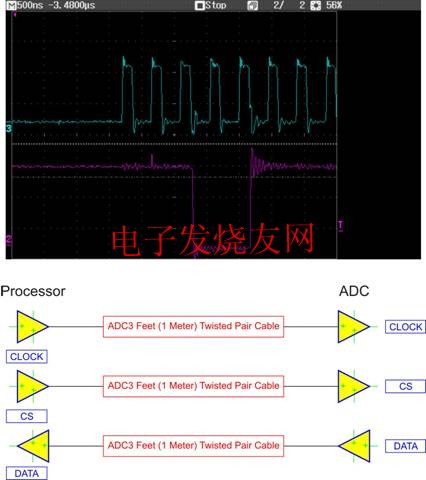

图 1 ADC 处理器时钟信号 (CH3) 和处理器上 ADC 的数据信号 (CH12)。可在线获取该系统的结构图。

图 1 中,设计人员并未注意线路阻抗。该图显示了系统中 ADC 的测得结果。ADC 和处理器均位于其各自的板上,设计人员只是简单地通过一条 1 米长的 CAT-5 双绞线将两块板连接到一起。在图 1 中,处理器的时钟信号频率 (CH3) 为 2.25 MHz。该 ADC 使用这一信号来将数据传输同步回处理器 (CH2)。

最初,设计人员认为这两个器件之间的慢时钟速度不会引起端接问题。然而,时钟和数据信号端接方法会形成许多超出规定高电平和低电平阈值(过冲和下冲)的信号,存在错误边缘(振铃)的信号并降低操作余量(弱化眼图)的信号。

IBIS 仿真来帮忙!在您将电路实现为硬件以前可节省时间并降低成本。在进行原型设计以前,您对某种设计进行仿真时,厂商提供的 IBIS 模型以及您电路板的模型都是您工具箱中有用的东西。信号完整性问题对您的高速系统和低速系统都会产生影响。利用早期阶段的仿真电路分析,您可以给您的系统施加许多不同的条件,以防止并检测常见信号完整性问题。

关于布线技巧与EMC就介绍完了,您有什么想法可以联系小编。