今天小编要和大家分享的是EDA,IC设计相关信息,接下来我将从基于DDR2和DDR3的PCB信号完整性设计和注意事项解析,关于ddr3信号扇出和走线问题解析-文章-硬件设计-pcb这几个方面来介绍。

EDA,IC设计相关技术文章基于DDR2和DDR3的PCB信号完整性设计和注意事项解析

摘要

本文章主要涉及到对DDR2和DDR3在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关技术,其中一些设计方法在以前已经成熟的使用过。

1. 介绍

目前,比较普遍使用中的DDR2的速度已经高达800 Mbps,甚至更高的速度,如1066 Mbps,而DDR3的速度已经高达1600 Mbps。对于如此高的速度,从PCB的设计角度来讲,要做到严格的时序匹配,以满足波形的完整性,这里有很多的因素需要考虑,所有的这些因素都是会互相影响的,但是,它们之间还是存在一些个性的,它们可以被分类为PCB叠层、阻抗、互联拓扑、时延匹配、串扰、电源完整性和时序,目前,有很多EDA工具可以对它们进行很好的计算和仿真,其中Cadence ALLEGRO SI-230 和Ansoft’s HFSS使用的比较多。

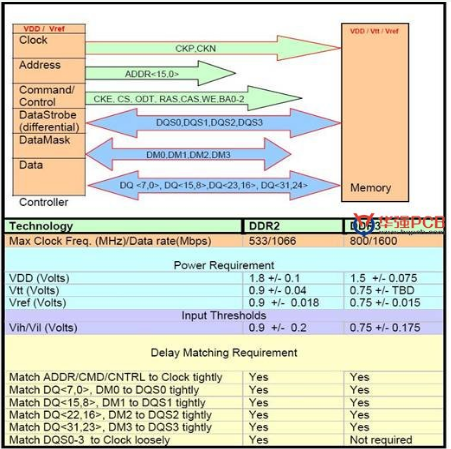

表1: DDR2和DDR3要求比较

表1显示了DDR2和DDR3所具有的共有技术要求和专有的技术要求。

2. PCB的叠层(stackup)和阻抗

对于一块受PCB层数约束的基板(如4层板)来说,其所有的信号线只能走在TOP和BOTTOM层,中间的两层,其中一层为GND平面层,而另一层为 VDD 平面层,Vtt和Vref在VDD平面层布线。而当使用6层来走线时,设计一种专用拓扑结构变得更加容易,同时由于Power层和GND层的间距变小了,从而提高了PI。

互联通道的另一参数阻抗,在DDR2的设计时必须是恒定连续的,单端走线的阻抗匹配电阻50 Ohms必须被用到所有的单端信号上,且做到阻抗匹配,而对于差分信号,100 Ohms的终端阻抗匹配电阻必须被用到所有的差分信号终端,比如CLOCK和DQS信号。另外,所有的匹配电阻必须上拉到VTT,且保持50 Ohms,ODT的设置也必须保持在50 Ohms。

在 DDR3的设计时,单端信号的终端匹配电阻在40和60 Ohms之间可选择的被设计到ADDR/CMD/CNTRL信号线上,这已经被证明有很多的优点。而且,上拉到VTT的终端匹配电阻根据SI仿真的结果的走线阻抗,电阻值可能需要做出不同的选择,通常其电阻值在30-70 Ohms之间。而差分信号的阻抗匹配电阻始终在100 Ohms。