今天小编要和大家分享的是EDA,IC设计相关信息,接下来我将从如何使用IBIS模型来确定PCB板的信号完整性问题,pcb设计 信号完整性分析这几个方面来介绍。

EDA,IC设计相关技术文章如何使用IBIS模型来确定PCB板的信号完整性问题

本文是关于在印刷电路板(PCB)开发阶段使用数字输入/输出缓冲信息规范(IBIS)模拟模型的文章。本文将介绍如何使用一个IBIS模型来提取一些重要的变量,用于信号完整性计算和确定PCB设计解决方案。请注意,该提取值是IBIS模型不可或缺的组成部分。

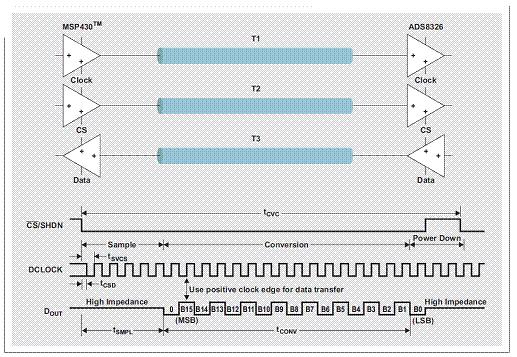

图 1 错配端接阻抗PCB装置

信号完整性问题

当观察传输线两端的数字信号时,设计人员会吃惊于将信号驱动至某条 PCB 线迹时出现的结果。通过相对较长的距离,相比瞬时变化信号,电信号更像行波。描述电路板上电波行为的较好模拟是池中波 (wave in a pool)。纹波穿过池顺利传播,因为体积相同的两组水具有相同的“阻抗”。然而,池壁的阻抗差异明显,并以相反方向反射波。注入 PCB 线迹的电信号也出现相同的现象,其在阻抗错配时以类似方式反射。图 1 显示了错配端接阻抗的一个 PCB 装置。微控制器即 TI MSP430™ 向 TI ADS8326 ADC发送一个时钟信号,其将转换数据发送回 MSP430。图 2 显示了该装置中阻抗错配所形成的反射。这些反射在传输线迹上引起信号完整性问题。让一端或者两端的 PCB 线迹电阻抗相匹配可极大地减少反射。

图 2 图 1 中错配端接阻抗促发反射

要解决系统电阻抗匹配问题,设计人员需要理解集成电路 (IC) 的阻抗特性,以及起到传输线迹作用的 PCB 线迹的阻抗特性。知道这些特性,让设计人员能够将各连接单元建模为分布式传输线迹。

传输线迹为各种电路服务,从单端和差分端器件到开漏输出器件。本文主要介绍单端传输线迹,其驱动器有一个推拉输出电路设计。图 3 显示了用于设计该举例传输线迹的各组成部分。

图 3 实例单端传输线电路