今天小编要和大家分享的是存储技术相关信息,接下来我将从浅谈3D NAND Flash技术未来的走向及发展趋势,flash 绘制稿这几个方面来介绍。

存储技术相关技术文章浅谈3D NAND Flash技术未来的走向及发展趋势

2020年5月17日-20日举行了在线IMW(International Memory Workshop),笔者自2018年起已经连续三年参加IMW会议,而在线会议还是首次参加。今年的会议中,有关3D NAND的论文数量最多,因此,笔者就各家NAND型闪存(以下简称为:“NAND”)厂家的现状、未来的技术蓝图(Roadmap)展开论述。

NAND的历史

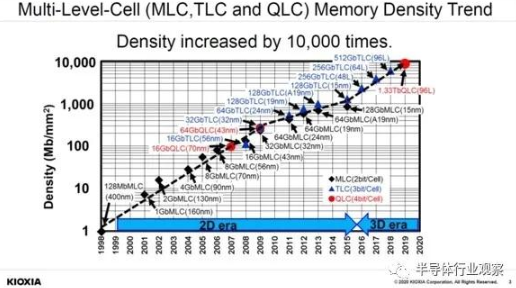

5月17日的会议(Tutorial)“PART I - 3D NAND”中,首位出场的是铠侠(原东芝存储半导体)的Noboru Shibata先生,他在主题为《History and Future of Multi-Level-Cell Technology in 2D and 3D Flash Memory》的演讲中,说明了NAND的历史,如下图1。

图1:NAND存储密度增加的趋势。(图片出自:Noboru Shibata, KIOXIA Corp., “History and Future of Multi-Level-Cell Technology in 2D and 3D Flash Memory”, IMW2020, Tutorials PART 1.)

Noboru Shibata先生以NAND的字位(Bit)为焦点,如上图1展示了2字位(MLC)、3字位(TLC)、4字位(QLC)分别对应了何种细微性、何种存储容量的芯片。

在2009年(32纳米)以后,存储半导体密度的增长趋势呈现了一时的放缓现象,自2016年开始转向3D趋势,且趋势越来越明显。因此,人们普遍期待未来3D化的NAND将会继续扩大存储的密度。

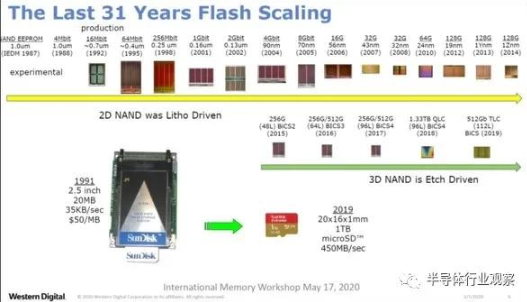

Shibata先生的演讲之后,WD的Yan Li先生做了题目为《3D NAND Architecture and its Application》的演讲,其中提到31年来NAND的细微化全过程。如下图2所示。

图2:NAND存储密度增加的趋势。(图片出自:Yan Li, Western Digital Corporation, “3D NAND Architecture and its Application”, IMW2020, Tutorials PART 1.)

1987年在IEDM上公布的NAND的细微化为1um。此次的发言者应该是NAND的发明人—舛冈富士雄先生(笔者推测),在次年的1988年,以1um生产出了4M bit的NAND,1992年以0.7um发布了16M bit。自此,东芝的NAND业务开始正式启动。