TTL与非门电路结构怎么看

几十年前,半导体技术相对落后,人们为了组成逻辑电路,都是利用二极管(D)与三极管(T)来组成DTL逻辑电路。随着半导体集成电路技术的不断提升,人们把与门的输入端的二极管取消了,直接利用多发射极半导体三极管来代替二极管(D),于是就产生了TTL(三极管T与三极管T)与非门电路。

与非门电路是由与门电路和非门电路结合组成的。

与门电路的特性是,只有当所有的输入都为高电平时,才有信号输出的的电路叫与门电路。

所谓“非门”电路,实际上是一个共发射极开关放大器(俗称;反相器)。

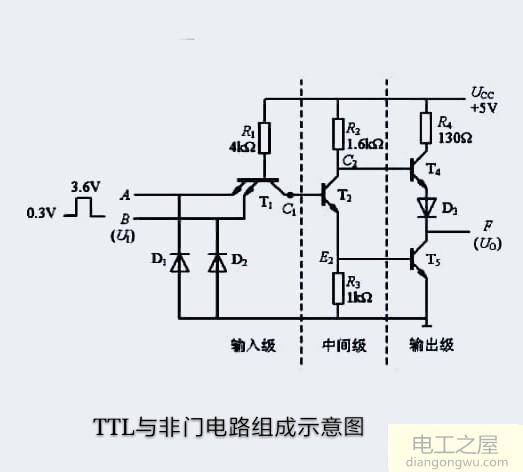

与非门电路,它由三部分组成。(详细见下图)

①输入级;输入级由多发射极晶体管T1,二极管D1、D2和电阻R1组成。

②中间级;中间级由T2,R2和R3组成。T2的集电极、C2和发射极E2分别提供两个相位相反的电压信号。

③输出级;输出级由D3、T4、T5和电阻R4组成。T4与T5组成一个推挽式输出结构电路。它具有较强的负载能力。

从电路结构示意图来了解,TTL与非门不难看出;与非门电路的输入端至少有一个(假设A端)接低电平,0.3Ⅴ,(B点输入为3.6V高电平)。T1晶体管的A端发射结导通,UB1=UA+UBE1=1V,其它发射结反向偏置截止。因为UB1=1Ⅴ,所以T2,T5截止,UC2≈Ucc,T4晶体管工作在放大状态,于是电路中的F点(Uo)输出高电平(5-0.7-0.7)Ⅴ=3.6Ⅴ。

当T1的输入端(A、B两点)

全接入高电平,即T1,UB1=UBc1+UBE2+UBE5=0.7ⅹ3=2.1Ⅴ时,T1的发射结反向偏置,集电极正向偏置,它工作在倒置放大状态,并且T2,T5三极管工作在饱和状态下,T4,UC2=UcEs2+UBE51≈1Ⅴ截止,T5处于深度饱和状态,则电路F(Uo)输出为低电平,Uo=0.3V。

当输入端A、B全部接高电平时,则F点(Uo)输出为低电平。T1→处于倒置放大状态,T2→处于饱和状态,T4→处于截止状态,T5→处于深度饱和状态。

当输入端至少有一个接为低电平时,输出Uo则为高电平,T1→处于深度饱和状态,T2→处于截止状态,T4→处于放大状态,T5→处于截止状态,由此可见,电路的输出与输入之间满足TTL与非门电路的逻辑关系,(F=AB)。