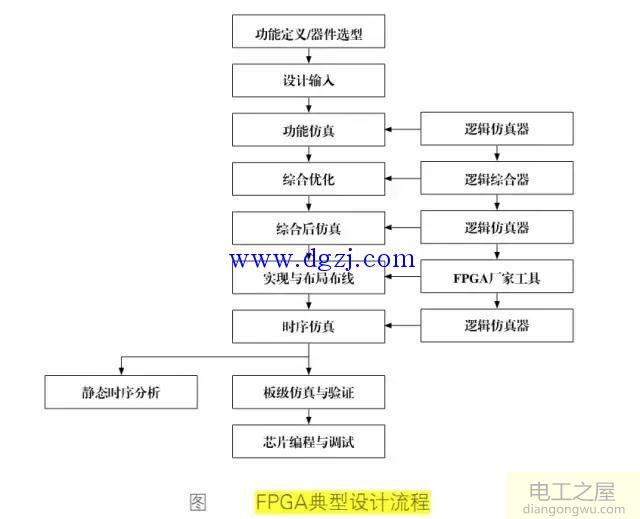

FPGA可编程逻辑器件设计流程

通常可将FPGA/CPLD设计流程归纳为以下7个步骤,这与ASIC设计有相似之处。

1.设计输入。Verilog或VHDL编写代码。

2.前仿真(功能仿真)。设计的电路必须在布局布线前验证电路功能是否有效。(ASCI设计中,这一步骤称为第一次Sign-off)PLD设计中,有时跳过这一步。

3.设计编译(综合)。设计输入之后就有一个从高层次系统行为设计向门级逻辑电路设转化翻译过程,即把设计输入的某种或某几种数据格式(网表)转化为软件可识别的某种数据格式(网表)。

4.优化。对于上述综合生成的网表,根据布尔方程功能等效的原则,用更小更快的综合结果代替一些复杂的单元,并与指定的库映射生成新的网表,这是减小电路规模的一条必由之路。

5.布局布线。

6.后仿真(时序仿真)需要利用在布局布线中获得的精确参数再次验证电路的时序。(ASCI设计中,这一步骤称为第二次Sign—off)。

7.生产。布线和后仿真完成之后,就可以开始ASCI或PLD芯片的投产