pwm的工作原理及8051中的pwm模块设计

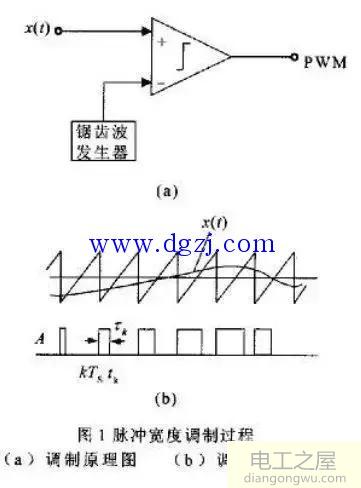

脉冲宽度调制波通常由一列占空比不同的矩形脉冲构成,其占空比与信号的瞬时采样值成比例。图1所示为脉冲宽度调制系统的原理框图和波形图。该系统有一个比较器和一个周期为Ts的锯齿波发生器组成。语音信号如果大于锯齿波信号,比较器输出正常数A,否则输出0。因此,从图1中可以看出,比较器输出一列下降沿调制的脉冲宽度调制波。

通过图1b的分析可以看出,生成的矩形脉冲的宽度取决于脉冲下降沿时刻tk时的语音信号幅度值。因而,采样值之间的时间间隔是非均匀的。在系统的输入端插入一个采样保持电路可以得到均匀的采样信号,但是对于实际中tk-kTs

(1)

其中,x{t}是离散化的语音信号;Ts是采样周期;是未调制宽度;m是调制指数。

然而,如果对矩形脉冲作如下近似:脉冲幅度为A,中心在t=kTs处,Tk在相邻脉冲间变化缓慢,则脉冲宽度调制波Xp(t)可以表示为:

(2)

其中 。无需作频谱分析,由式(2)可以看出脉冲宽度信号由语音信号x(t)加上一个直流成分以及相位调制波构成。当T0

。无需作频谱分析,由式(2)可以看出脉冲宽度信号由语音信号x(t)加上一个直流成分以及相位调制波构成。当T0

数字脉冲宽度调制器的实现:

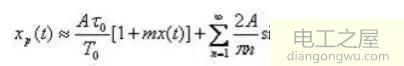

实现数字脉冲宽度调制器的基本思想参看图2。

图中,在时钟脉冲的作用下,循环计数器的5位输出逐次增大。5位数字调制信号用一个寄存器来控制,不断于循环计数器的输出进行比较,当调制信号大于循环计数器的输出时,比较器输出高电平,否则输出低电平。循环计数器循环一个周期后,向寄存器发出一个使能信号EN,寄存器送入下一组数据。在每一个计数器计数周期,由于输入的调制信号的大小不同,比较器输出端输出的高电平个数不一样,因而产生出占空比不同的脉冲宽度调制波。

图3

为了使矩形脉冲的中心近似在t=kTs处,计数器所产生的数字码不是由小到大或由大到小顺序变化,而是将数据分成偶数序列和奇数序列,在一个计数周期,偶数序列由小变大,直到最大值,然后变为对奇数序列计数,变化为由大到小。如图3例子。

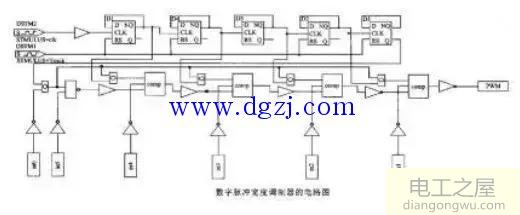

奇偶序列的产生方法是将计数器的最后一位作为比较数据的最低位,在一个计数周期内,前半个周期计数器输出最低位为0,其他高位逐次增大,则产生的数据即为偶数序列;后半个周期输出最低位为1,其余高位依次减小,产生的数据为依次减小的偶序列。具体电路可以由以下电路图表示:

8051中的PWM模块设计:

应该称为一个适合语音处理的PWM模块,输出引脚应该外接一积分电路。输出波形的方式适合作语音处理。设计精度为8位。

PWM模块应包括:

1、比较部分(Comp):

2、计数部分(Counter):

3、状态及控制信号寄存/控制器(PWM_Ctrl);

1)状态积寄存器:(Flags),地址:E8H;

①EN:PWM模块启动位,置位为„1‟将使PWM模块开始工作;

②(留空备用)

③④解调速率标志位:00–无分频;01–2分频;10–10分频;11–16分频。(RESET后为00)

⑤(留空备用)

⑥(留空备用)

⑦(留空备用)

⑧(留空备用)

注意:该寄存器可以位操作情况下可写,不可读;只能在字节操作方式下读取。

2)数据寄存器(DataStore),地址:F8H;注意:该寄存器值不可读,只可写。

4、端口:

1)数据总线(DataBus);(双向)

2)地址总线(AddrBus);(IN)

3)PWM波输出端口(PWMOut);(OUT)

4)控制线:

① CLK:时钟;(IN)

② Reset:异步复位信号;(IN低电平有效)

③ WR:写PWMRAM信号;(IN低电平有效);

④ RD:读PWMRAM信号;(IN低电平有效)

⑤ DONE:接受完毕反馈信号;(OUT高电平有效)

⑥ INT:中断申请信号;(OUT低电平有效)

⑦ IntResp:中断响应信号;(In低电平有效)

⑧ ByteBit:字节/位操作控制信号(IN1-BYTE0-BIT);

⑨⑩中断占用相当于MCU8051的外部中断2,则可保证在5个指令周期之内,“读取数据”中断必定得到响应。

PWM模块使用方法:因为占用了8051外部中断1,所以在不使用该模块时,应该把外部中断2屏蔽。而PWM模块产生的中断请求可以看作是“能接受数据”的信号。中断方法如后“中断读取数据过程”。使用PWM模块,应该先对内部地址8FH的数据寄存器写入数据,然后设置地址8EH的状态寄存器最低位(0)为1,即PWM模块开始工作并输出PWM调制波(如TIMER模块)。在输出PWM调制波过程中,应及时对PWM写入下一个调制数据,保证PWM连续工作,输出波形连续。

中断读取数据过程:

1.PWM模块可以读取数据,申请中断信号INT置位为„0‟,等待8051响应;

2.8051接受到中断申请后,作出中断响应,置位IntResp信号线为„0‟;

3.PWM模块收到IntResp信号后,把中断申请信号INT复位为„1‟,等待8051通知读取数据WR信号;

4.8051取出要求数据放于数据总线(DataBus)上,并置WR信号为„0‟;

5.PWM模块发现WR信号为„0‟,由数据总线(DataBus)上读取数据到内部数据寄存器,将DONE位置位为„1‟;

6.8051发现DONE信号的上跳变为„1‟,释放数据总线;

7.PWM模块完成当前输出周期,复位DONE为„0‟,从此当前数据寄存器可以再次接受数据输入。

注意事项:

1)输出的PWM信号中的高电平部分必须处于一个输出周期的中间,不能偏离,否则输出语音经过低通后必定是一失真严重的结果。

2)对于8位精度的PWM,每个输出周期占用256(28)个机器周期,但是包含256个机器周期至少有22个指令周期,亦即264(22*12)个机器周期,由于语音信号的连续性,256与264之间相差的8个机器周期是不能由之丢空的,否则也会使输出信号失真。如果将须输出数字量按256/264的比例放大输出,亦不可行,因为如此非整数比例放大,放大倍数很小,则经过再量化后小数部分亦会被忽略掉,产生失真。举例:输出数字量为16,按比例放大后为16.5,更会产生难以取舍的问题。

故采取以下办法:该模块以时钟周期为标准,而与TMBus无关,即基本上与8051部分异步工作。读取数据方式为每次读取足够数据段储存于模块内的RAM内(暂定每次读取8字节),储存字节数必须能保证PWM输出该段数据过程中,有足够时间从RAM处继续读取数据。由于占用了8051的外部中断2,中断申请在3个指令周期(36个时钟周期)内必定能得到响应,而PWM模块处理一个数据需要固定耗时256个时钟周期,故能保证PWM模块顺序读取数据中断能及时得到响应,不会影响调制信号的连续性。

3)RDRAM过程是异步过程。

4)输出后数据寄存器不自动清零。因为可以通过把Flags(0)写„0‟而停止PWM模块继续工作。