今天小编要和大家分享的是74ls373,锁存器相关信息,接下来我将从锁存器74ls373应用电路图大全(四款抢答器/单片机接口/信号发生器电路),用373锁存器连接数码显示管和51单片夹,373的锁存控制这几个方面来介绍。

用373锁存器连接数码显示管和51单片夹,373的锁存控制

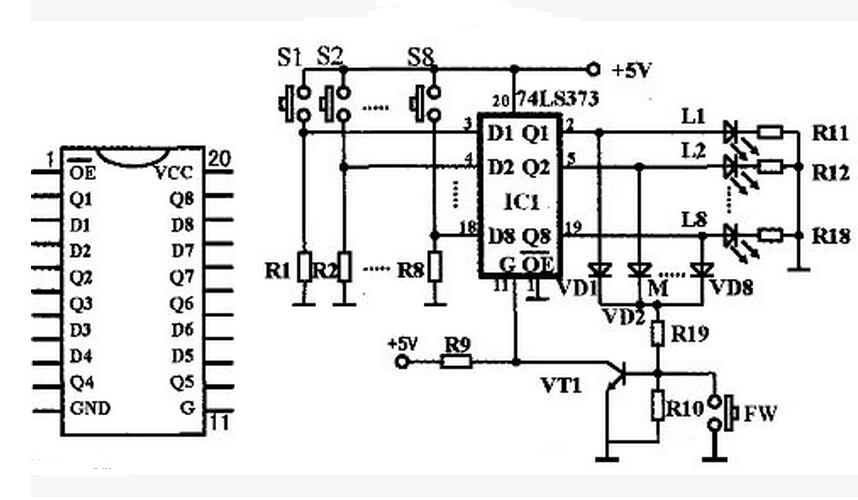

锁存器74ls373应用电路一:抢答器电路

利用74LS373设计的抢答器电路它由一片8D锁存器74LS373。8只组别按键开关S1-S8,8组别抢答有效的状态显示发光二极管L1-L8,一个复位按键FW等组成。该8路竞赛抢答器,每组受控于一个抢答按键开关,高电平表示抢答有效。

设置主持人控制键FW用于控制整个系统清0和抢答有效开始控制的启动。每按下一次复位键FW时,使8D锁存器的控制端G为高电平,若组别按键开关S1~S8中任何一个都没按下,即对应8D锁存器的输入端D均为低电平,则此时8个输出端均为低电平,对应的发光二极管均不点亮,表示抢答者正在准备抢答状态。按下复位键FW时,8D锁存器的控制端G为高电平,若组别按键开关S1-S8中存在一个或几个处于按下状态,即与之对应的8D锁存器的输入端D为高电平,此时与之对应的8D锁存器的输出端立即为高电平,对应的发光二极管被点亮,表示抢答者违规了。只有每按下一次复位键FW,并在复位键FW抬起后,抢答才是有效的。

系统具有第一抢答信号鉴别和锁存功能。在主持人将系统复位并使抢答 有效开始后,第一抢答者按下抢答按钮。对应的输入引脚接高电位1,8D锁存器的对应输出端立即为高电平1。二极管VD1-VD8组成了或门电路。使三极管VT1基极得到高电位而饱和导通使锁存器的G为低电平,将8D锁存器的输入信号锁存在了输出端,输入端的信号变化将不在影响输出端。对应点亮的发光二极管指示出第一抢答者的组别。在显示有效的组别的同时,也可同时采用蜂鸣器警示。

器件选择与电路制作:

8D锁存器选择74LS373,其引脚排列图如图2示。若选择其它型号的,要注意控制端电平的要求,及其它的使能端。8只组别按键开关S1-S8、复位按键FW可选择AN8系列车床控制用按钮。8组别抢答有效的状态显示用发光二极管L1~L8选用φ10的高亮LED;三极管VT1选择S9014,电阻R1-R8选择025W/5.1kΩ,R11~R18选择~25W/430Ω,R9和R10选择0.25W/5.1kΩ,R19选择0.25W,5,10Ω,二极管VDl~VD8选择IN4148。

电路采用单5V电源供电,制作时可使用7805稳压集成电路获得。制作时,抢答按键、指示LED可通过接线端子从线路板上引出,方便于使用。组装焊接无误,即能保证可靠工作。

设计特点:

8D锁存器74LS373的允许端G的控制信号不是周期固定的脉冲信号,而是将取自锁存器输出端的信号处理后得到的,保证电路结构最简洁、处理时间最快捷,同时减少了脉冲源存在可能带来的干扰,使电路性能更可靠。

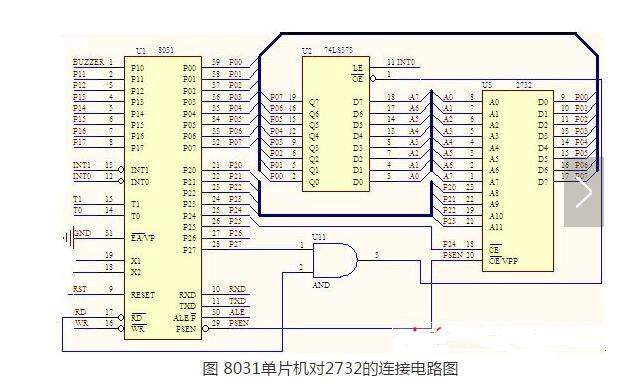

锁存器74ls373应用电路二:单片机连接电路

8031经地址锁存器74LS373与2732的接口电路连接图如图所示。2732是4KB的EPROM型器件,即其存储容量为4KB。

根据2732的存储容量,确定8031片内地址线为P2.3~P2.0和P0.7~P0.0,共12条。如下图所示:P2.3~P0.0直接与2732的A11~A8相接,P0.7~P0.0经74LS373输出后接到2732的A7~A0 。

根据片内地址线确定片选地址线,则8031的片选地址线共四条:P2.7~P2.4。如图3.2所示:P2.4直接与2732的/CE相连(即当P2.4=0时,选通2732);8031的/RD和P2.7经过一个与门与74LS373的/OE相连(即/RD=0且P2.7=0时,选通74LS373);P2.6、P2.5悬空。/PSEN和2732的/OE相连,以便8031执行MOVC指令时产生低电平而选中2732工作。

根据基本地址范围的定义,2732的基本地址范围为:0000H-0FFFH

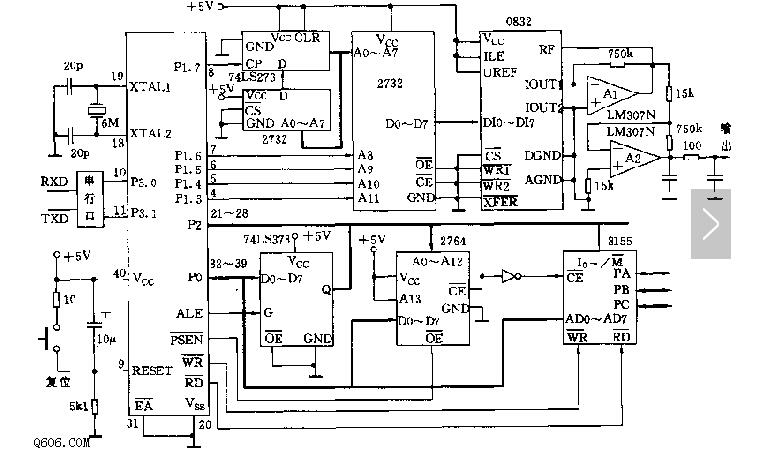

锁存器74ls373应用电路三:正弦波信号发生器

为了能够产生一个可程控的、且具有一定幅度、频率精度高、波形失真小的正弦波,这里采用了一种新方法一离散存储法来实现原理电路图如图所示。由8031单片机电路、信号产生部分、开发应用部分组成。信号产生部分包括柔性计数器、只读存储器、D/A转换器、放大滤波器;开发应用部分包括地址锁存器、只读存储器、扩展I/O口。

1、8031附属电路

XTAL1、XTAL2为单片机8031内部振荡电路的引出脚。外接作为反馈元器件的晶体、电容--并联谐振回路构成自激振荡器,输出时钟脉冲。安装时,晶体、电容应尽量靠近单片机芯片,以减小寄生电容,更好地保证振荡器的工作稳定性。

P3口是一个双向I/O口,有8位(P3.0~P3.7)。在MCS-51中,有8个引脚还用于专门功能,这些功能如下表。

串行接口RS232是一个全双工通信接口,能同时进行接收和发送。若只能发送或接收的称为单工;若可以发送和接收,但不能同时进行的,称为半双工。

RESET是复位引脚。5.1k电阻为下拉电阻,复位开关控制片内复位电路的工作。

2、信号产生部分

信号产生部分中,柔性计数器是个新内容,下面单独进行介绍。

(1)柔性计数器:由74LS273 8D锁存器和2732 EPROM程序存储器组成。8D锁存器的8位D触发器用作状态寄存器,并提供计数器的输出信号。2732EPROM用作产生反馈函数。在时钟脉冲未到来前,D触发器处于某一输出状态,并选中2732EPROM的某一存储单元;当8031的P1.7端输出一个CP时钟脉冲时,该存储单元中的数据便送到D触发器,使74LS273变为新的状态,接着又选中2732EPROM 新的存储单元;如此反复地进行。当计数器出现自启动时,解决的办法是将那些不应出现的计数输出所对应的EPROM存储单元都写入0000.这样,无论进入那一个非正常状态,下一个CP总能自动地使计数器恢复到正常工作状态。

柔性计数器具有下列优点:

a、可实现多种计数功能,硬件电路却不需变动,而是由EPROM中的编码决定某种具体功能。 b、较易实现某些特殊功能。 c、电路功能较难剖析,保密性较好。

(2)工作原理:根据测试系统的要求,由8031单片机先对要产生的正弦波形进行离散化求值。再按一定的比特(bit)取整数,由8031的P1.6~P1.3输出存放到2732 EPROM 中。存储器可分段存储波形的离散函数值;再由8031计算出定时时间,控制相应的脉冲,这些脉冲控制柔性计数器的循环,计数器每次计数的结果作为2732 EPROM 的输入地址。

EPROM输入的高四位A11、A10、A9、A8作为地址选择。当选择64等分时,其存储内容正好对应于64个等分点,柔性计数器也选择64次计数,这样每次计数输出的内容作为EPROM的输入值。对应每一个EPROM的输入,如输入为20H,硬件应会自动在内部查找地址的20H单元。在地址为20H单元中,存放的是对应于等分点为20H时的函数值,Y=sin360X/64.

每一个存储单元存放的是经过扩大后的16进制数,因此,EPROM输出到D/A转换器的也就是该扩大值Y‘,Y’=127Y+127.此关系式是考虑到正弦波的负半周在进行放大时,必然会导致存储单元中要存放负整数,这是不允许的。由于扩大数据倍数为127,于是采用先将正弦波整个都提高127,这样就可使所有数据都不出现负值,从而保证了EPROM的正常工作。EPROM相应的地址单元输出一个对应的离散函数值送入DAC 0832.转换器采用完全直通方式,使内部两级寄存器的输出都跟随输入数据变化,工作速度较快。输入的数字量可直接进入8位转换器转换成模拟电流,再通过A1运算放大器对总电流求和并变成模拟信号电压。然后经过电压运算放大器和帕型滤波器,用以消除DAC 0832转换过程中产生的尖峰干扰和毛刺,便可输出所需要的正弦波信号。

本信号发生器在10Hz~1kHz范围内的频率可精确程控,波形失真度小于2%(采用示波器观测波形时,能观察出的波形失真度一般在5%以上。)

在测试过程中,若要增大输出正弦信号的幅度,可再增加运算放大器的级数。若对帕型滤波后的波形还不够满意,可以接入一级采样保持电路。采样保持电路的输出只响应每次D/A转换输出的最终值,从而滤除了转换过程中产生的干扰和毛刺。

本仪器具有自动检测功能。当使用写入命令写入EPROM时,每写完一个单元后,立即可读出该单元的内容。若发现读出内容和写入的不符,会即刻停止。在2732存储器中,可分段存储多种波形函数,通过选择高位地址,可控制得到所需要的波形,如锯齿波、正弦波、三角波等。

(3)开发应用部分(控制部分)

8031的数据总线口P0还兼作外部存储器(2764)的低8位地址线,于是只能分时用作地址线,放采用地址锁存器(74LS373)锁存。只有当地址锁存信号(ALE)的下降沿来到时,地址输出才有效,所以74LS373的使能端G和8031的ALE相连,其输出允许端OE‘接地。

P0口是单片机应用系统中快用最为频繁的通道口。数据总线要和74LS373、2764、8155相连接,而在同一瞬间内只能选通其中的一个芯片,这时总线传递的数据只对选通的芯片有效。芯片的片选端由地址总线控制。

8031的片外取指信号PSEN’和EPROM的输出允许端相连接。读取片外程序存储器(2764)中的指令或数据。8031的P0口可直接用于外部存储器的数据进行读/写传送。片选端CE‘由8031的高地址线控制。8155扩展I/O口是可编程的并行I/O扩展接口芯片,具有扩展其它外围功能电路的复合功能。在8031单片机中虽然有四个I/O口,但可供用户使用的I/O四只有P1口和部分P3口。因此,在开发应用系统中需要进行I/O口的扩展。所以利用8155扩展I/O口,以便实现单片机通过通用接口母线GPIB系统对显示器、打印机、键盘和驱动开关等的控制。

8155的片选端CE’极其内部RAM的选择端IO/M‘由8031的高位址线控制。当IO/M’=0时,选择8155的I/O接口。本信号发生器通过GPIB、PS232接口可方便地接到自动化测试系统中。

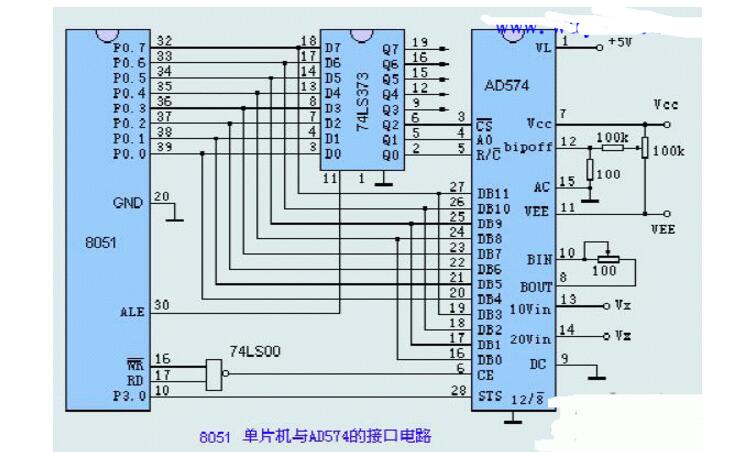

锁存器74ls373应用电路四:单片机接口电路

AD转换器的数据输出也通过PO数据总线连至8051,由于我们只使用了8位数据口,12位数据分两次读进8051,所以接地。当8051的p3.0查询到STS端转换结束信号后,先将转换后的12位A/D数据的高8位读进8051,然后再将低4位读进8051。

这里不管AD574A是处在启动、转换和输出结果,使能端CE都必须为1 ,因此将8051的写控制线和读控制线通过与非]74LS00与AD574A的使能端CE相连。

关于74ls373,锁存器就介绍完了,您有什么想法可以联系小编。