今天小编要和大家分享的是乘法器,模拟乘法器相关信息,接下来我将从乘法器电路设计方案汇总(五款模拟电路设计原理及仿真程序分享),乘法意义 乘法的性质 分数乘法 乘法计算方法 乘法器 模拟乘法器这几个方面来介绍。

乘法意义 乘法的性质 分数乘法 乘法计算方法 乘法器 模拟乘法器

本文为大家介绍五款乘法器电路设计方案,包括五款模拟电路设计原理及仿真程序分享,以供参考。

乘法器电路设计方案一:简易两位二进制乘法器设计

设计原理:

1、基本公式: A1 A0 * B1 B0=Y3 Y2 Y1 Y0

2、设计理念: 两位二进制数 A1 A0 和B1 B0 相乘后,结果最高为四位Y3 Y2 Y1 Y0

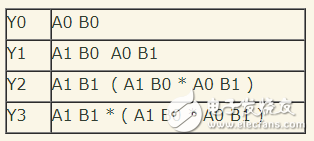

3、归纳得出:由上式可归纳得出输出的4位二进制数与输入的两位二进制数之间的逻辑,得出下表:

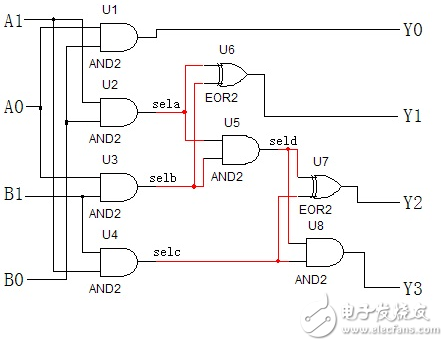

逻辑电路图

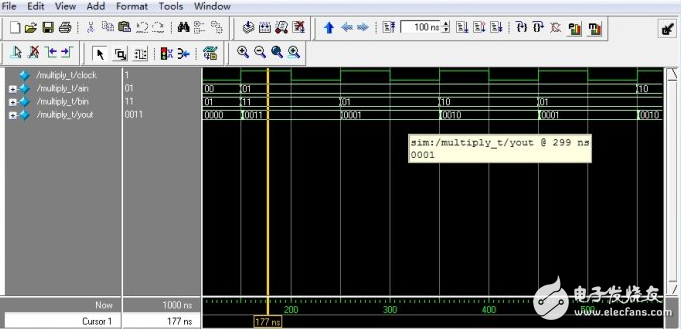

仿真波形图

乘法器电路设计方案二:十六位硬件乘法器电路设计

利用硬件箱自带16进制码发生器,由对应的键控制输出4位2进制构成的1位16进制码,数的范围是0000~1111,即0H~FH.每按键一次,输出递增1,输出进入目标芯片的4位2进制数将显示在该键对应的数码管。

乘数和被乘数的输入模块将16进制码的A~F码设计成输出为null.使得减少了无用码的输入。 两数相乘的方法很多,可以用移位相加的方法,也可以将乘法器看成计数器,乘积的初始值为零,每一个时钟周期将乘数的值加到积上,同时乘数减一,这样反复执行,直到乘数为零。本设计利用移位相加的方法使得程序大大简化。

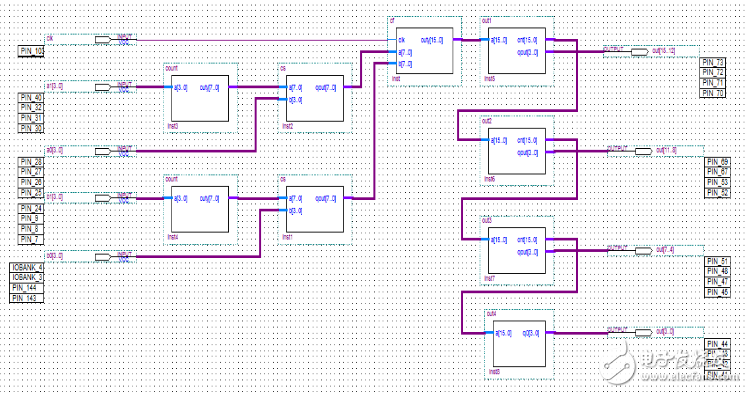

系统总体电路组成原理图如下图所示:

乘法器电路设计方案三:8位并行乘法器

串行乘法器,通常是两个N位二进制数x、y的乘积用简单的方法计算就是利用移位操作来实现。但计算一次乘法需要8个周期,这种乘法器的优点是所占用的资源是所有类型乘法器中最少的,在低速的信号处理中有着广泛的应用,但是串行乘法器速度比较慢、时延大。程序设计

VHDL代码

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_ARITH.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

entity chengfa is

port( clk :in std_logic;

a :in std_logic_VECTOR(7 downto 0);

b :in std_logic_VECTOR(7 downto 0);

cout:out std_logic_VECTOR(15 downto 0) );

end chengfa;

architecture one of chengfa is

signal a1,b1:std_logic_vector(3 downto 0);

signal a2,b2:std_logic_vector(7 downto 4);

signal cout1:std_logic_vector(15 downto 0);

signal cout2:std_logic_vector(15 downto 0);

signal a1b1,a2b1,a1b2,a2b2:std_logic_vector(15 downto 0);

begin

process(a,b,clk)

begin

if clk‘event and clk=’1‘ then

a1b1《=“0000”&(a(5 downto 0) *b(5 downto 0));

a2b1《=“00”&(a(7 downto 6)*b(5 downto 0))&“000000”;

a1b2《=“00”&(a(5 downto 0)*b(7 downto 6))&“000000”;

a2b2《=(a(7 downto 6)*b(7 downto 6))&“000000000000”;

end if;

end process;

process(clk)

begin

if clk’event and clk=‘1’ then

cout1《=a1b1+a2b1;

cout2《=a1b2+a2b2;

end if;

end process;

process(clk)

begin

if clk‘event and clk=’1‘ then

cout《=cout1+cout2;

end if;

end process;

end one;

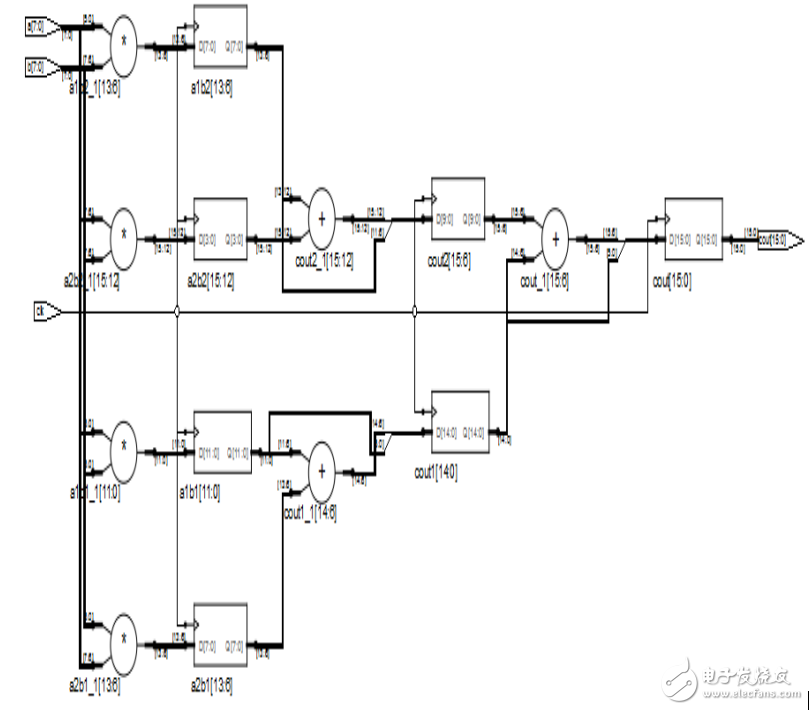

8位并行乘法器RTL图

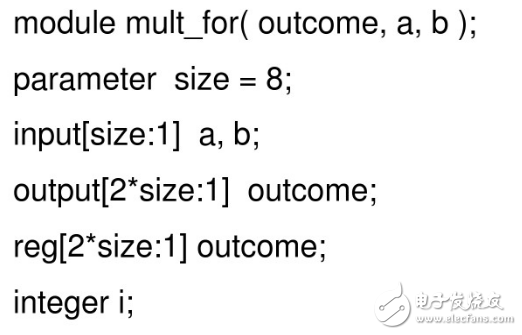

乘法器电路设计方案四:移位相加乘法器

程序设计

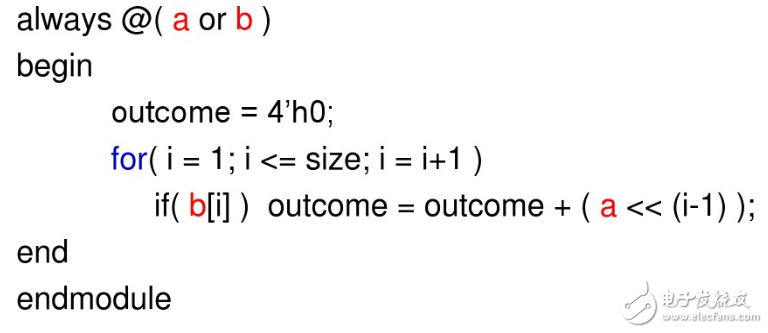

仿真波形图

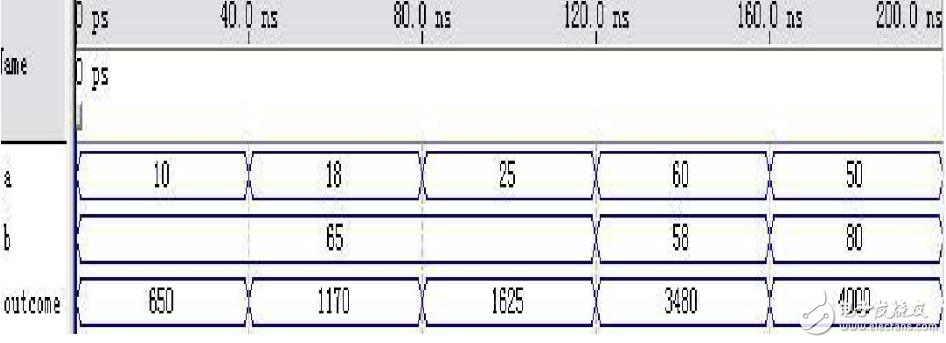

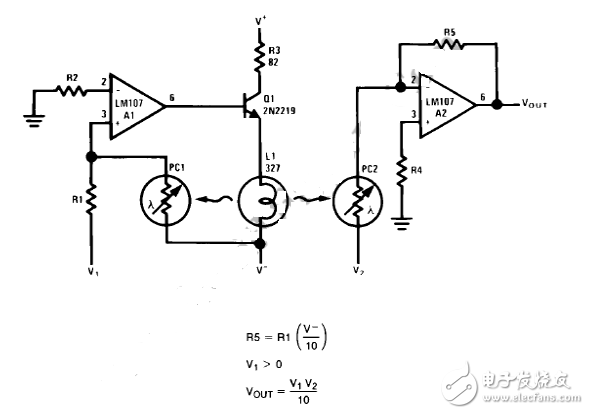

乘法器电路设计方案五:模拟乘法器设计

下图显示了一个简单的模拟乘法器体现。该电路提供了三个象限模拟乘法。

关于乘法器,模拟乘法器就介绍完了,您有什么想法可以联系小编。