今天小编要和大家分享的是运放,阻塞,消除电路图相关信息,接下来我将从运放阻塞以及消除电路图,运放的阻塞现象及其消除措施-其他电源电路图-电子这几个方面来介绍。

运放,阻塞,消除电路图相关技术文章运放阻塞以及消除电路图

集成运放出现阻塞现象时,放大电路将失去放大能力,相当于信号被运放阻断一样。正反馈将导致输入级一直处于饱和状态,输入信号将不能正常输出,这就造成了阻塞现象。

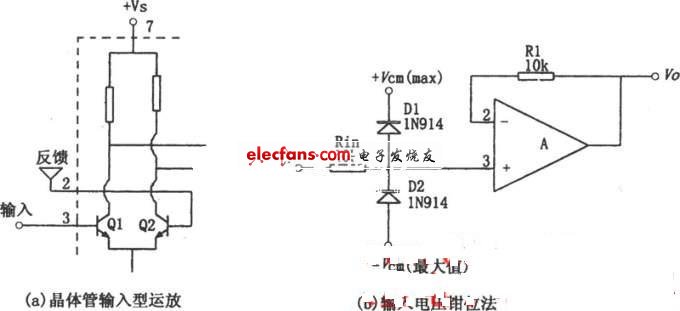

为了进一步说明阻塞现象的成因,举例如下:图(a)为晶体管输入型运放的输入级电路,现假定共模输入电压范围小于+8V,并假定输出信号的电压振幅为+14V。若运放接成电压跟随器,参见图(b),现有一个大于8V的信号加于同相输入端(对应③脚),当输入信号处于正半周时,输出电压Vo也为正值,这个电压Vo经反馈加在输入差动放大电路Q2的基极,此时Q2将处于饱和导通状态(集电结处于正向偏置),因此+Vs通过Q2的集电极电阻直接加在运放的输出端,使运放出现阻塞现象。一旦发生阻塞,只能采用切断电源的方法来破坏正反馈。即为恢复运放正常工作,需暂时切断电源。这种阻塞现象具有极大的危险性,它可能使器件迅速损坏,其原因是:由图(a)知输入级采用NPN型晶体管组成差动放大电路,由于输入信号幅度超过共模电压的允许范围,电路将在信号正峰值时出现阻塞,若信号源内阻较低,反馈电阻也较小,流过Q2集电结的电流就过大,有可能烧坏晶体管Q2,使集成运放损坏。另外,在输出端上不论什么原因产生的输出瞬时过压也会造成阻塞现象。

消除阻塞现象的方法一般可分为两类:限制输入电压法和防止输出瞬时过压法。图(b)所示电路即为限制输入电压钳位法,图中±Vcm为共模输入电压上、下限极限值,运用二极管D1和D2实现将输入电压钳位在±Vcm之间。这个方法具有通用性。当运放的电压放大倍数大于l时,其钳位电平值应降低相应的倍数。

关于运放,阻塞,消除电路图就介绍完了,您有什么想法可以联系小编。