同时,为了准确获取标签信息,必须将读写器与PC机相连。读写器通过由FPGA实现的串口模块与PC机相连,对读取到的标签信息做必要的显示,如标签返回的RN16、EPC、UII等。

4、FPGA实现电路

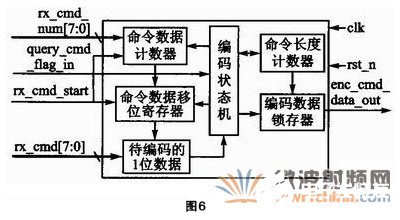

为了实现FPGA部分的功能,在Altera公司的EP1C3T100C6芯片上,利用Quartus II软件进行设计,PIE编码模块设计如图6所示。

图6 PIE编码模块设计框图

4.1编码模块设计

PIE编码由pie_encode模块实现。该模块接收命令产生模块并行发来的8位数据,按照协议规定及设置,先给命令数据添加特定的帧头,并根据数据传输速率,对命令数据及其CRC5/16校验位进行PIE编码,编码完成后输出给射频发射模块调制,然后通过天线发送出去。其设计框图如图6所示。

PIE编码模块由编码状态机作为控制模块。状态机的状态由命令帧头和数据0和1组成,即idle、delimiter、tari、rtcal、trcal、data_ sendl、data_send0 7个状态,其中idle是空闲状态,接收到开始信号后跳转到其他状态。状态机的流程按照命令的组成依次进行,每个状态按照协议要求保持特定的时间,直至命令编码完成。由于Query命令和其他命令的帧头不同,query_cmd_flag_in信号用于指示此次发送来的数据是否为Query命令数据,如果是,则在编码时加入TRcal命令段;否则,跳过TRcal状态。