通信处理器支持通用数据包格式。数据包格式非常灵活,并且完全可编程,从而确保了它与专用数据包的兼容性。在发送模式下,可以配置通信处理器以便为存储在数据包RAM内的有效负载数据添加前同步码、同步字和CRC。在接收模式下,通信处理器可以在接收前同步码、同步字、地址与CRC时检测和中断主处理器,并将接收的有效负载存储到数据包RAM内。ADF7023-J采用由MAC级中断和PHY级中断(可以单独设置)组成的高效中断系统。可以利用Manchester或8b/10b编码对有效负载数据和16位CRC进行编码/解码。换句话说,可以使用数据白化和反白化。

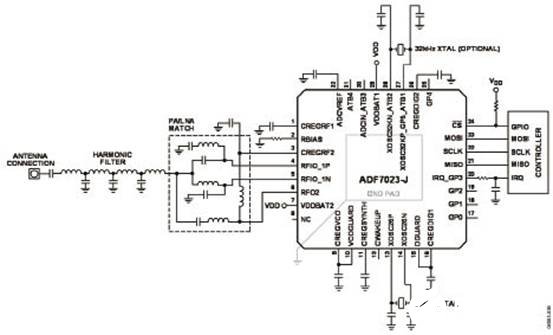

图3 ADF7023-J典型应用电路图

利用内部唤醒定时器,SWM能够自发地将ADF7023-J从休眠状态唤醒,而无需主处理器进行干预。唤醒之后,ADF7023-J受控于通信处理器。这种功能可以在主处理器处于休眠状态时实现载波感应、数据包侦探和数据包接收,从而降低了系统总电流消耗。满足中断条件时,智能唤醒模式可以将主处理器唤醒。可以对这些中断条件进行配置,包括接收有效前同步码、同步字、CRC或地址匹配。还可以利用主处理器触发将器件从休眠模式唤醒。对于那些需要高精度唤醒时序的系统而言,32kHz振荡器可用于驱动唤醒定时器。换句话说,可以使用内部RC振荡器降低休眠模式下的电流消耗。