ADF7023-J采用具有硬件加速功能的AES引擎,提供了128位分块加密/解密,密钥长度为128位、192位和256位。

支持电子源码书(ECB)和密码链块模式1(CBC模式1)。AES引擎可用于给包数据加密/解密,也可被主处理器用作独立加密/解密引擎。在ADF7023-J上,可以通过下载AES固件模块来启动AES引擎,进而对RAM进行编程。片上8位ADC提供了外部模拟输入读回、RSSI信号或集成式温度传感器。只要电池电压降至用户定义的阈值以下,集成式电池电压监控器就会向主处理器发出中断标志。

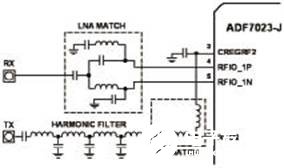

图4 ADF7023-J分离的单端PA和LNA匹配电路图

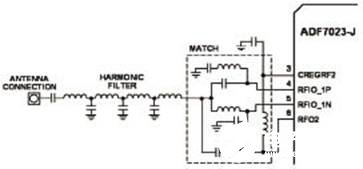

图5 ADF7023-J组合的单端PA和LNA匹配电路图

ADF7023-J的主要特性

• 超低功耗、高性能收发器

• 频带:902 MHz ~958MHz

• 支持的数据速率:1 kbps ~300kbps

• 电源电压范围:1.8 V ~3.6V

• 单端和差分功率放大器(PA)

• IF带宽可编程的低IF接收器

• 100kHz、150kHz、200kHz和300kHz

• 接收器灵敏度(BER)

- 1.0kbps,2FSK和GFSK下, 灵 敏度为116dBm