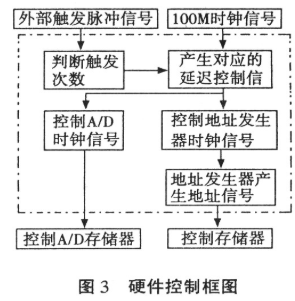

本设计选用CPLD器件MAX7128S实现对高速数据采集系统的控制,硬件框图如图3所示。

虚线框内的是硬件逻辑控制模块,该模块可以完成我们所设计的高速数据采集所需的A/D转换器和存储器的控制信号。

2.3.1 控制逻辑的实现

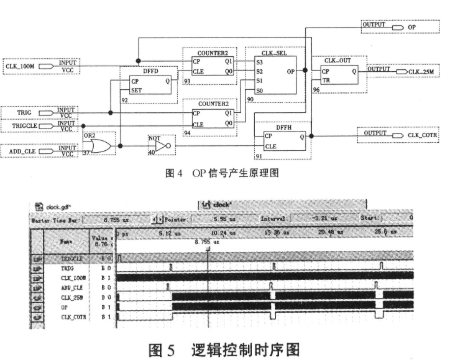

高速数据采集控制逻辑的实现主要是通过两个两位的计数器来实现的,连接TRIG(触发启动信号)的计数器(启动计数器)是判断当前是第几个脉冲,它的状态过程是:00→0l→10→ll,连接100MHz晶体振荡器的计数器(晶振计数器)来统计10ns的个数,就是说当连接触发启动信号的计数器从00→0l时,晶振计数器是00状态,这时后面的状态选择输出一个由低到高的跃变OP,控制后面25MHz数据采集开始,当启动计数器又有一个触发过来,它就从0l→10,这时晶振计数器就开始从00→0l,也就是统计一个10ns,统计完了以后,后面的状态选择又输出一个由低到高的跃变OP,开始25MHz数据采集。以后依次类推,分别是延迟20ns和30ns开始数据采集。

原理图如图4所示。

2.3.2 地址的生成

在逻辑控制设计完成后,将最后得到的25MHz的时钟输入17位计数器,每次上升沿到来,地址加1,生成的地址信号使得采集的信号存入对应的地址单元。使用Q9位是为了让输出端可以产生低电平,从而在采集的数据到达所需个数时有一个上升沿来触发其所控制的触发器,使得数据采集暂停,等待下一次采集;12作反馈,它指示的是数据采集到了4k,通过它进行反馈,用它停止A/D芯片的工作,同时将地址计数器清零,准备数据读出;最后,存储够了4k的数据,AD_0E输出高电平,用于控制A/D芯片和内部地址计数器,可以看到地址计数器在数据采集到达4K后也清零,在初始的位置等待数据的读出。系统控制原理图如图6所示。系统仿真结果(仿真图略)表明,该设计可以满足本系统要求。