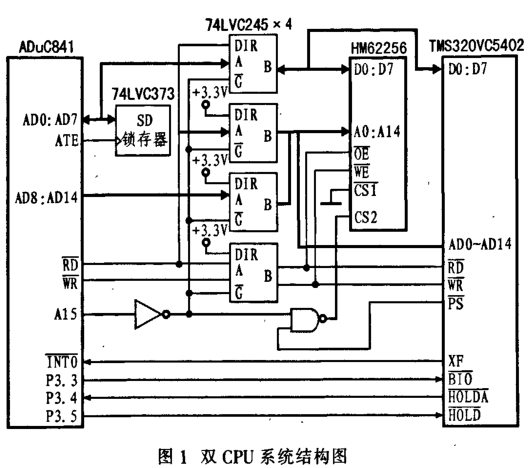

考虑上述问题,采用ADuC841与TMS320VC5402的双CPU系统结构如图1所示。存储器HM62256既是TMS320VC5402的全局数据存储器,又是ADuC841的外部存储器。A15为片选信号,地址范围为8000H~FFFFH。两个CPU分别通过总线和数据存储器HM62256相连,实现存储器共享。

隔离电路采用4片74LVC245双向缓冲器实现,由于ADuC841的P0口是分时复用的地址/数据总线,所以需采用一片74LVC373地址锁存器将P0端口的地址信号从地址/数据总线中分离出来。而ADuC841的16位数据总线需要双向缓冲,由于ADuC841要对HM62256进行读写操作,所以缓冲器的方向由ADuC841的读信号RD控制,当ADuC841读数据时,RD为低电平,使数据缓冲方向为HM62256至ADuC841;写数据时,RD为高电平,数据缓冲方向为ADuC841至HM62256。缓冲器的使能线由A15反向信号控制,当A15为高电平时,选通缓冲器,否则缓冲器为高阻态。A15还是HM62256的片选信号,若要ADuC841和TMS320VC5402都能选通HM62256,需将A15和PS的与非信号作为HM62256的片选信号。ADuC841选通时,PS为高电平,ADuC841的A15有效。TMS320VC5402选通时,当A15为低电平时,PS有效。

ADuC841通过P3.5、P3.2(INT0)分别与TMS320VC5402的HOLD、XF引脚相连,P3.5向TMS320VC5402申请总线控制,TMS320 VC5402响应ADuC841的请求后,HOLDA信号变低,TMS320VC5402的CPU挂起,并出让外部总线。ADuC841通过A15打开总线驱动器,并经与非门后选中HM62256,获得HM62256的控制权,实现对HM62256的读写操作。而TMS320VC5402可通过XF向ADuC841请求中断,ADuC841在响应中断INT0后,通过P3.5将HOLD信号转换为高电平,此时总线控制权重新交给TMS320VC5402。