该文采用的CPLD 是Altera 公司的MAX7000S系列的EPM7128SQL100-10。它有84 个引脚,其中5 根用于ISP(IN System Programmable)下载,可方便的对其进行“在系统”编程。EPM7128SQL100-10支持对电压工作,可以利用Altera 公司的第四代开发平台quartus Ⅱ方便地进行仿真、综合和下载。

2 硬件接口电路设计

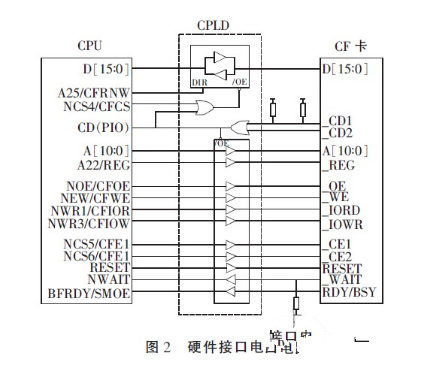

硬件接口电路的电路图如图2 所示。在此电路中用CPLD 来实现一般CF 卡接口电路中的双向缓冲器和与非门等一些逻辑器件的逻辑功能,使接口电路变的更为简单、稳定、高速,而且可以通过现场修改程序来实现不同的功能。

CF 卡中的_CD1、_CD2 是CF 卡是否安装的状态检测信号,在CF 卡中接地。当CF 卡没有安装时,电路中_CD1、_CD2 由上拉电阻将其输出拉为高电平;当CF 卡安装时,_CD1、_CD2 由CF 卡接地输出为低电平,_CD1、_CD2 相当于CF 卡的总开关。在实际接口电路中_CD1、_CD2 要接10 kΩ 的上拉电阻。

将片选任务寄存器的CS4A 编程为1 则可使能EBI 的复用引脚NCS4/CFCS、NCS5/CFCE1、NCS6/CFCE2 为CompactFlash 信号CFCS、CFCE1、CFCE2,使能NOE/NRD/CFOE、NWR0/NEW/CFWE、NWR1/NBS1/CFIOR、NWR3/NBS3/CFIOW、A25/CFRNW为Compact Flash 信号CFOE、CFWE、CFIOR、CFIOW、CFRNW。这样就可以通过访问保留给NCS4 的地址空间来访问外部的CF 卡。在NCS4 的地址空间中用当前的传输地址来分辨I/O 模式,通用存储模式是标志存储模式。传输地址总线的A23 用作I/O 模式选择。该文CF 卡用A22/REG 来分离通用存储模式和标志存储模式。

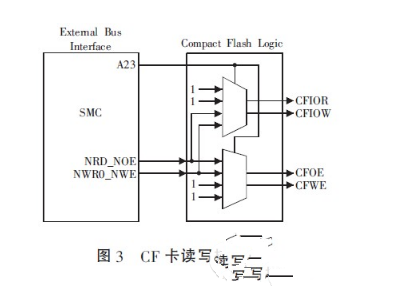

在I/O 模式下,CompactFlash 的逻辑驱动CFIOR与CFIOW 信号上SMC 的读写信号,此时CFOE 与CFWE 信号失效。同样在通用存储模式和标志存储模式下驱动CFOE 与CFWE 信号上的SMC,CFIOR与CFIOW 信号失效。该逻辑如图3 所示。

CFOE 与CFWE 通过CPLD 和CF 卡的OE 与WE连接起来,这是CF 卡在Memory Mode 的读写使能。

CFIOE 与CFIOW 通过是I/O Mode 的使能。除了使能信号外,其他的信号对2 种模式都是相同的。

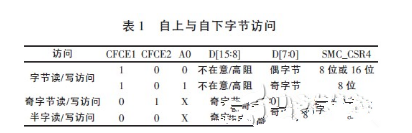

CFCE1 与CFCE2 信号使能CF 卡的数据总线由上或是由下访问,具体信息见表1。只有当NCS4 引脚上的SMC 配置为驱动8 位存储器时才可进行奇字节访问,NCS4 地址空间中的片选寄存器必须如表1所示进行设置。