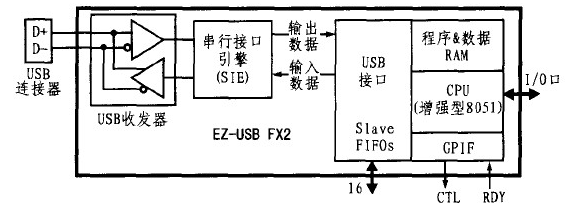

图1 56 脚CY7C68013 的体系结构

3、硬件设计

图2 所示是FPGA 与CY7C68013 的连接图, 除将IFCLK作为FPGA 输入时钟外,其它信号均在FP2GA 和CY7C68013 之间互连。由于FPGA 片内RAM很小, 本系统还使用了一片128k ×8 的高速静态RAM(型号为IS63LV1024 , 读写周期为15ns) 作为数据暂存器。FPGA 与CY7C68013、RAM、VT6103 的硬件连接见图2。

图2 硬件连接总图

从USB 收到的来自上位PC 机数据最终将被远端安装在LED 显示屏屏体内的显示控制部件中, 当RAM被填入预定数量的显示数据时, FPGA 会从RAM中连续取出数据并送到与VT6103 连接的4 位数据输出端口, VT6103 收到4 位数据后, 其内部会自动按照IEEE802. 3 规范对该数据进行4B5B(转换4 位数据数据码为5 位数据码) 重新编码,然后将5B码送扰频器,再经片内整形后输出给以太网变压器,以驱动五类双绞线并将数据传给远端显示控制部件。

4、软件设计

本系统的外部主设备接口逻辑采用VHDL 硬件描述语言,利用ALTERA 公司QUARTUS II 开发平台进行设计。软件设计是以FPGA 为核心的,主要由下面3 个并行执行的部分组成, 在此每个部分分别设计为一个VHDL 进程(process) :

进程1 : 外部主设备FPGA 同步读写CY7C68013“大”端点FIFO 的时序逻辑, 并把接收到的数据存入FPGA FIFO 中。这部分只需要根据Slave FIFO 读写时序进行设计,Slave FIFO 时序图如图3 所示。

图3 Slave FIFO 同步读时序

这里需要引起注意的是两个建立时间: 其一是tOEon , 这个建立时间是从SLOE 拉低到Slave FIFO 数据有效。其二是tSRD ,即从SLRD 信号拉低到第1 个同步读时钟上升沿的时间。这两个建立时间应大于等于CY7C68013 数据手册规定的时间。由于该FPGA有59904 bit 的片上RAM, 这里使用其中4k byte 的RAM来生成FIFO 结构,这样从Slave FIFO 同步接收到的USB 数据就可以直接存入FPGA 片上的4k FI2FO 中。图4 是此进程的设计流程图。

图4 进程1 设计流程

进程2 : 用于完成将FPGA 的FIFO 中数据写入128kB RAM的设计。只要FPGA 的FIFO 中有数据,则该进程启动, FPGA 会连续地把片内FIFO 中取出的数据存入片外128kB 的高速静态RAM( IS63LV1024) 中, 这个片外的128kB RAM分为两个64kB 区,两个区轮流接收来自FPGA 片内FIFO 的数据, 当一个区接收完规定的显示数据后, FPGA 会置位send data flag 去启动进程3 ,如果FPGA 片内FIFO中还有数据, 则FPGA 会把RAM切换到另一个区继续接收片内FIFO 中的数据,其设计流程图如图5 所示。