另一种数字IP自动生成则是针对更一般电路,它通常使用C/C++/SystemC等高级语言作为输入,其输出则是功能和高级语言输入等价的RTL/门级网表/GDS。这类数字自动生成工具通常又称作“high-levelsynthesis”(HLS)。HLS的优点和限制都很明确:优点是整体设计和验证速度都很快,省去了微结构设计和RTL编写的时间,验证上也可以直接和使用高级语言的系统验证方便地整合在一起。而其缺陷则在于高级语言在描述数字逻辑时的颗粒度较粗,且一般没有时序的概念,因此HLS生成的电路通常仅能保证功能正确,但是在电路的速度(往往由时序划分决定)和功耗(HLS对于常规的低功耗设计方法学如clockgating的支持还不方便)上比起手写的RTL可能有差距。在信号处理模块上,HLS生成的电路比起手写RTL差距较小,差距可以在20%以内,甚至在一些场合可以做到HLS生成的电路与手写RTL性能没有差距。目前,HLS的主要产品包括MentorGraphics的Catapult,Cadence的Stratus,Xilinx的VivadoHLS等。

HLS的概念提出已经有十多年,但是在最近得到了越来越多的重视。这除了和HLS本身技术发展之外,还和半导体行业的趋势有关。在过去,半导体芯片的主要范式还是大的半导体厂商提供通用的处理器平台,在这样的范式下,由于在计算平台上执行的算法不确定,因此半导体厂商的策略就是把通用处理平台的每一个细节都做到完美,这样一来自然就没有HLS的发展空间。而在最近,随着人工智能、大数据和下一代多媒体需求的出现,SoC上对于执行固定算法的数字IP的需求在大大增强,而且随着互联网厂商加入芯片战局也为半导体芯片快速交付提出了需求。在这种情况下,HLS就变得越来越有价值。这是因为,对于这类执行固定算法的数字信号处理IP,算法本身以及IP顶层架构的优化对于SoC芯片整体性能的影响往往远远大于具体电路实现带来的影响。在较短交付周期的限制下,如果使用传统的数字设计方法论,往往就意味着留给顶层架构和算法探索的时间比较少,最后导致使用高效的RTL代码实现了并非最优的架构/算法。反之,如果使用HLS,则可以大大压缩RTL设计的时间,这样就给架构/算法探索留下了更多时间,最后尽管HLS生成的电路性能可能比手写RTL要差20%,但是顶层架构/算法的优化带来的影响可能是2-3倍的性能提升,而HLS带来的time-to-market的改善则可能是更大的影响。

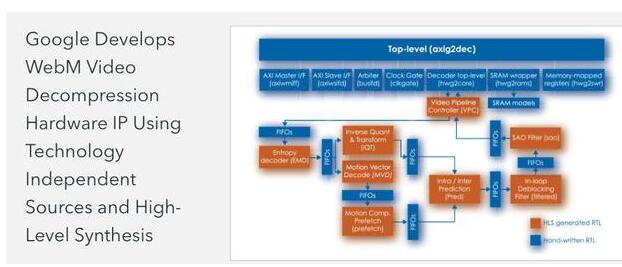

谷歌使用CatapultHLS实现了视频解码IP中的绝大部分模块。该IP是典型的数字信号处理IP。