模拟IP自动生成

在模拟电路领域,自动IP生成也是EDA领域的一个热门方向。

模拟IP自动生成目前能做的是给定一种电路结构(例如带4-tapDFE的wirelinereceiver)和模块指标,自动生成电路图和版图并完成仿真验证。在未来,随着电路库中电路结构数量的上升,也有机会能实现仅需输入模块功能和指标,IP自动生成器可以自主选择最优电路结构并生成符合指标的电路和版图。

模拟IP自动生成可以分成两部分,即自动调优电路中的晶体管参数和自动生成版图。前者至少有30年的历史,上世纪九十年代就有不少学者在研究用各种数学优化方法来自动选择模拟电路中晶体管的参数。在今天,如果仅仅是选择电路中的晶体管参数而不考虑自动生成版图,那么常规的EDA工具中的参数扫描就能满足大部分需求。但是,电路图设计中的晶体管参数自动调优往往不能落实到实际设计中,这是因为随着半导体工艺越来越先进,模拟电路中的版图效应也越来越显著,而电路图设计中的晶体管参数调优并不能反映版图的影响,因此往往扫描得到的电路图最优晶体管参数和版图设计完成后的最优参数有一定差别。因此常见的做法是先做一个版本电路图设计,然后去画版图并做带版图效应的电路仿真,然后再去调整电路图设计中的晶体管参数。在这个过程中,即使电路图中的晶体管参数都能自动化调优,但是整体的设计流程还是卡在了手工画版图——仿真——调整电路图晶体管参数这个循环里。

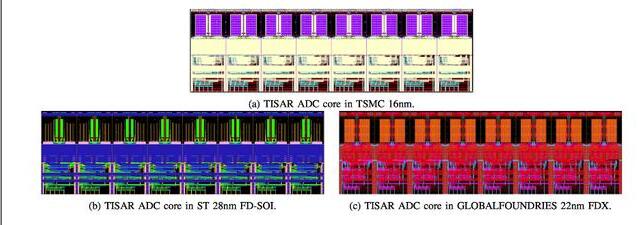

而模拟IP自动生成解决的最大痛点,就在于能自动生成版图。这样一来,整体的流程都可以做到自动化,仅需输入指标,生成器可以自动生成一组晶体管参数,自动生成版图做仿真,并自动根据版图仿真结果去调整电路图晶体管参数。这就大大节省了模拟IP生成的人力和时间,并提升了设计效率。目前,模拟IP自动生成做的最领先的是UCBerkeley的BAG(BerkeleyAnalogGenerator)项目,该项目已经能自动生成SerDes、ADC等复杂的模拟/混合信号IP的电路设计和版图,并且在28nm和16nm等先进工艺下都得到了流片验证。

BAG自动生成的ADC版图

自动IP生成是中国EDA的机会

自动IP生成在美国得到了相当的重视,美国国防高级研究计划局(DARPA)2019年的电子复兴计划(ERI)中,自动IP生成(IDEA)是其重点扶持方向之一。我们认为,这个领域对于中国的半导体行业有重要价值,同时中国距离全球先进的差距也并不大,因此如果得到足够支持的话有机会能在未来数年内追赶全球领先。