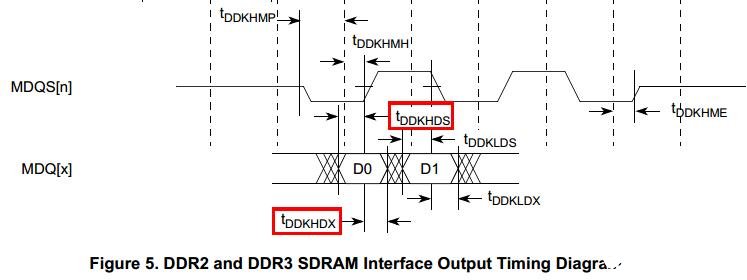

下面我们通过具体实例来看看时序的计算,下图是Freescale MPC8572 DDR主控芯片手册,这张图片定义了从芯片出来的时候,DQS与DQ之间的相位关系。

图10 MPC8572时序图

图11 MPC8572时序参数

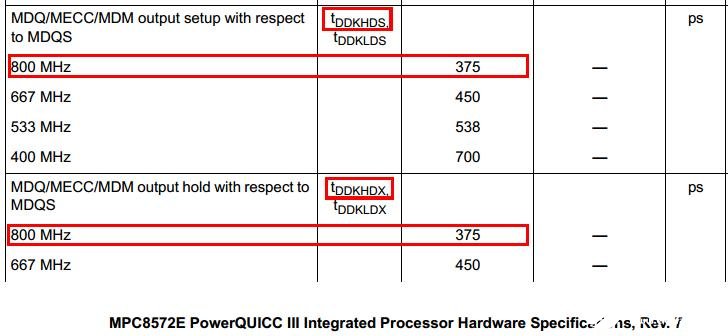

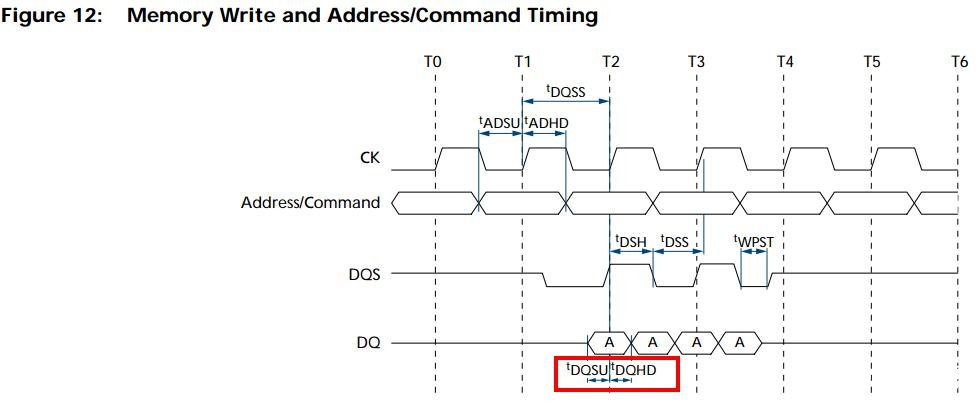

颗粒端为美光DDR,该芯片的时序图以及时序参数如下图所示,这张图片则定义了颗粒端芯片识别信号所需要的建立时间与保持时间。

图12 DDR颗粒时序图以及时序参数

我们用T_pcbskew来表示DQ与DQS之间的延时偏差,如果想要得到足够的时序裕量,则延时偏差要满足以下关系:

T_pcbskew《T_vb-T_setup

T_pcbskew》T_hold-T_va

代入数据,有:

T_vb-T_setup=375-215=160ps

T_hold-T_va=-160ps

这样,如果传输线的速度按照6mil/ps来计算,T_pcbskew为+/-960mil。大家会发现裕量很大,当然这只是最理想情况,没有考虑时钟抖动以及数据信号的抖动,以及串扰、码间干扰带来的影响,如果把这些因素都考虑进来,留给我们布线偏差的裕量就比较小了。

综上所述,时序控制的目的就是要保证数据在接收端有充足的建立时间与保持时间,明白了这一点,我们在线长匹配这个问题上就能做到胸有成竹,游刃有余了。

责任编辑;zl

关于EDA,IC设计就介绍完了,您有什么想法可以联系小编。