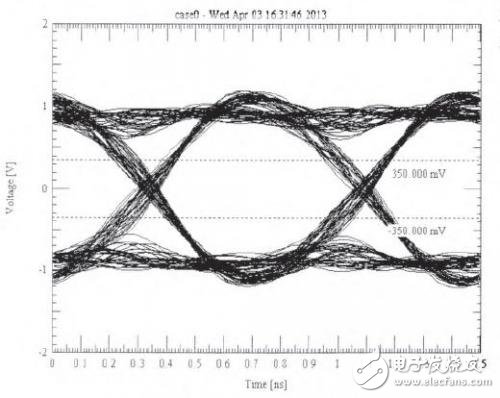

对8位数据总线DQ进行分析,选取一根数据线为受害线,其余数据线为反向伪随机码,条件设为最快驱动,在此最坏情况进行综合仿真,查看其受扰线的波形情况。

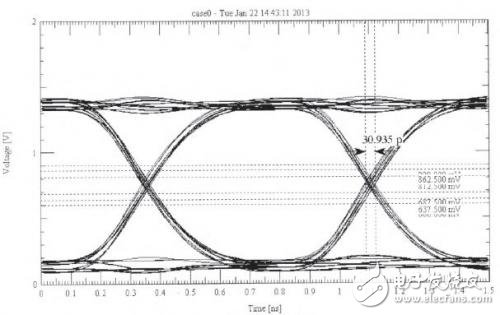

比较图5、图6后可看出此数据线受到各方面的因素综合影响,使波形眼图中的眼高和眼宽都相应减小,导致数据总线时序裕量大大减少。上述时序裕量需减去此值再考虑其他噪声因素,结合经验留些时序余量后,就可把时序余量转换成PCB设计时的布线长度约束(约6in/ns)。

图5 DO数据总线理想波形

图6 DQ数据总线最坏情况下的实际波形

4 PCB设计

4.1设计规则约束

(1)等长约束

采用分组等长方式,分组如下:

数据线与DQS、DM信号组:64位数据线按8位一组,每组分别对应其各自的DQS和DM信号;由于数据时序余量最小,组内严格控制延时,以对应的DQS为基准,等长精度在±10mil.

地址线、控制线、时钟线组:需等长控制,地址线与控制线各分支的误差±20mil,它们与时钟线误差在±100mil,差分时钟线之间±5rail.

(2)间距约束

DDR3同组线间的间距保持在2倍线宽;不同组类线的间距保持在3倍线宽;DDR3线与其他jBDDR3线之间的间距应大于50mil,用于串扰控制。

(3)线宽约束

根据传输线阻抗要求和印制板叠层结构计算走线线宽,设置走线线宽规则,保证阻抗的一致性。

4.2布线技巧

同组内总线尽量同层走线,时钟线与地层相邻;尽量少用过孔,如用需组内过孔数相同,保证其一致性;相邻信号走线需交叉,避免长距离的重叠走线,如相邻层间距足够大,可适当降低要求;

走线避免采用直角应用45.斜线或圆弧角走线;尽量采用3W原则走线;

与电源层相邻的信号层中的高速走线应避免跨电源\地平面;

电源层比地层内缩20H(H:电源层与地层的介质厚度);不允许有孤立铜的存在。

5 PCB板后仿验证

DDR3的PCB设计结束后进行后仿分析,用以对前面的仿真分析进行验证。PCB板后仿主要是对DDR3信号质量和时序关系进行分析。

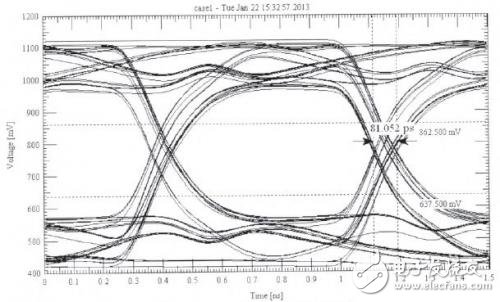

5.1 DDR3的差分时钟验证

DDR3差分时钟在PCB布线后对其后仿真分析,抽取一对实际时钟走线对所走链路进行分析其波形如下图7:其单调性和上下过冲都满足要求。