图7:差分时钟PCB走线波形图8数据总线写时序

5.2 DDR3的时序验证

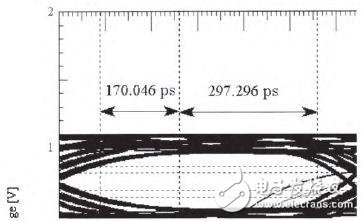

对于布线后的时序验证也是十分重要的环节。在确定好同步信号组及对应的选通信号后利用Cadence软件的BUS setup功能进行综合分析,位数据总线及相应的DQS信号,设定时钟频率666MHz,设定相应ibis模型,加入随机码流,最终进行分析后可通过测量得到时序参数可计算时序裕量,验证PCB布线是否满足相关的时序关系。分析结果见图8.

图8数据总线写时序

从上图8可测量出数据总线的建立时间和保持时间,根据DDR3数据相应时序进行静态时序计算,再综合考虑其余因素对时序的影响来估算包括其PCB走线长度引起的偏移等,满足其DDR3接收端的建立时间和保持时间的时序正确性,其它时序关系类似可通过此验证。

6结束语

通过上述Power PC模块的DDR3内存设计分析,了解高速信号反射、串扰、时序等因素对其设计的影响,其仿真分析成为增强计算机系统设计可靠性和稳定性的必要手段,为设计高速数字电路保驾护航。

来源;电子设计技术

关于EDA,IC设计就介绍完了,您有什么想法可以联系小编。