总之,我们要在设计理念上,提前介入研发,采用并行设计,采纳一板成功、减少研发次数的理念,加上诸如Cadence PSD的先进工具软件,我们不需要过度加班,更不需要两班乃至三班倒即可解决PCB的研发周期问题。

2.成本的挑战

PCB的成本包括显性成本和隐性成本

显性成本主要包括PCB的生产、贴片成本。

对于显性成本的控制,我们可以通过熟悉、了解常规板厂的工艺能力、贴片设备的工艺要求,选择合理的层数、设置合理的层叠结构、设计参数来降低PCB设计的显性成本。

隐性成本包括PCB设计期间的人员投入、技术风险、时间成本尤其是上市机会窗的机会成本。

而事实上,PCB设计的隐性成本远远大于其显性成本。

举例来说,一般手机的市场机会窗也就是半年左右,如果因为PCB设计的问题增加一次研发,对于流行时尚的手机产品来说带来的不仅仅是1-2个月的时间损失,更是整个产品的失败。

对于隐性成本的控制,公司高层和研发主管要具备抓紧核心、放开周边、强强组合、一次成功的理念,在设计之初考虑成本。合理借助外部资源,解决自身研发的短木板问题,降低产品研发的隐性成本。

3.高速的挑战

随着信号速率的不断提升,信号完整性不断困扰着研发人员,包括总线驱动能力、信号的反射、串扰、过冲、振荡、回沟、衰减等;有时也把时序划归到信号完整性范围内。Allegro中基于IBIS模型的仿真模块Signoise,可以方便地搭建拓扑进行仿真。

Allegro的这个仿真工具与布线平台有良好的接口,在PCB布线完成以后,还可以从PCB板上直接提取布线参数到Signoise平台中,进行后仿真以验证布线的效果。

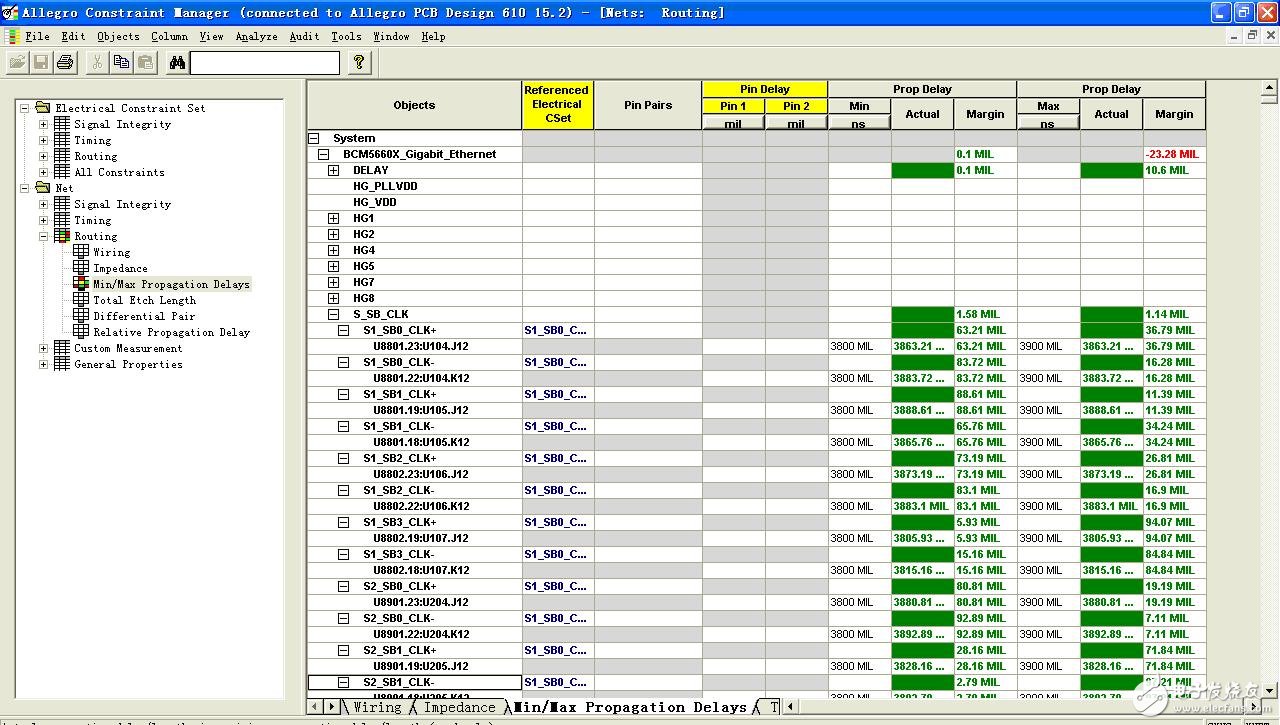

仿真提取的布线约束可以直接导入到Allegro的电气规则管理器中,这个管理器可以方便地对时序要求的等长规则进行约束,在布线时,当长度不符合所规定的规则时,Allegro可以实时进行告警。

图2:规则管理器示例(点击图片看大图)

如图所示,当长度在预定的范围之内的时候,表格中相应的区域显示绿色;当长度不在预定的范围内,不管是偏短还是偏长,表格的相应区域都显示为红色。

4.高密的挑战

我们来看看一组数据:

近年来器件封装的变迁:

过去20年IT行业单个器件PIN数目以及单块单板PIN总数的变迁: