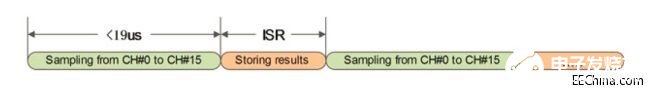

图2:16通道SAR采样。

图2显示的是基于DSI的多路复用器,能在多个输入之间自动切换当前的采样通道。图3显示的是硬件FIFO的概览图。

图3:用于缓冲采样结果的四个8字节FIFO。

配置SAR组件

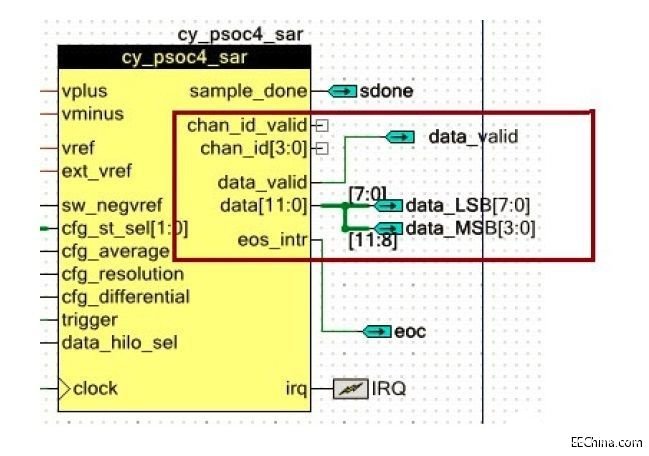

SAR被配置成单端模式采样单个输入通道,输入电压范围在0~Vdd之间,1MSps采样率。在收到采样触发信号后,SAR就开始输入信号采集,采集结束后产生一个“SDONE”信号,该信号被送入DSI网络,并被命名为“ADC_SDONE”。PSoC Creator标准组件库中提供的SAR组件无法支持输出采样结果到DSI总线上。因此,我们需要把SAR组件导入到项目中并加以修改,如图4中的红色部分所示。

图4:详细设计—修改SAR组件。

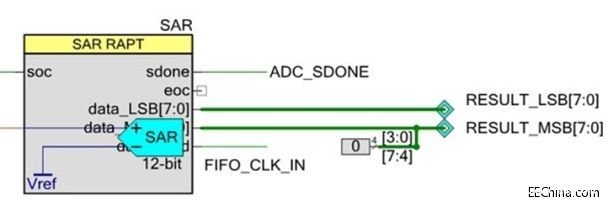

图5所示的是SAR组件的输出连接。在SAR_Start函数之后,我们还需要添加一行代码,使得SAR能将采样结果输出到DSI网络,如下所示:

// start SAR component and wait for conversion trigger

SAR_Start();?

// enable SAR sampling result output on DSI

*((reg32 *)(SAR_SAR_CHAN_CONFIG_IND + (uint32)(0 《《 2))) |=

SAR_DSI_OUT_EN;

图5:详细设计—SAR的输出连接。

基于DSI的多路复用器

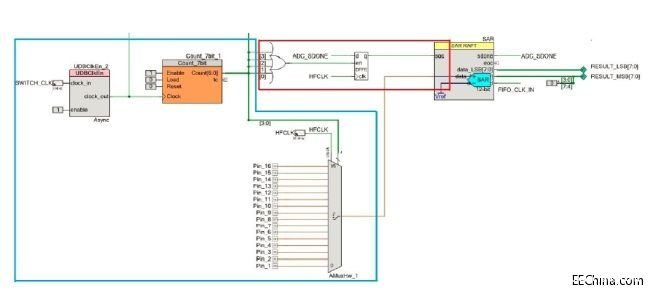

如图6中蓝色部分所示,通过DSI控制的硬件多路复用器取代SARMUX,以用于切换16个通道。采用SWITCH_CLK时钟触发Count7单元,以生成通道选择信号,这样每次通道转换可分为两个阶段:信号采集和转换。

图6:基于DSI的MUX和触发信号生成。

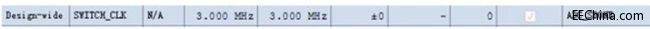

信号采集完成之后,信号将保持在SAR中,此时可切换输入通道。因此用于显示信号采集阶段完成的SDONE可用于通道切换。实际上,SWITCH_CLK是基于DSI信号“ADC_SDONE”(SDONE)定义的时钟,其设置见图6的“cydwr”页面。

图7:设计范围资源的时钟定义。