Count7单元属于定制组件,不在标准组件库的范围内。它是一个递减计数器,输出当前的计数器值给DSI。其默认值初始值为0x7F。因此通道选择的范围是从#15到#0。在主程序中添加以下代码实现对Count7的控制。

/* Enter critical section */

interruptState = CyEnterCriticalSection();

/* Set the Count Start bit */

MYCOUNT7_AUX_CTL |= (1 《《 5);

/* Exit critical section */

CyExitCriticalSection(interruptState);

// set default value of count7 as 0x7F

MYCOUNT7_COUNTER = MYCOUNT7_PERIOD;

生成SAR的采样触发

第1步:在完成当前采样工作之前生成下一个触发信号

由于针对SAR只有一个实际输入,因此一旦完成对当前通道的采样,SAR就需要为下一次采样触发信号。许多信号都适用于此目的,但触发信号选择应遵循以下两个规则:

1. 在触发信号和当前采样完成之间不应存在间隔,甚至触发信号可以提前发生,这样就可以降低延迟。

2. 触发信号必须确保不会破坏当前采样工作。

根据上述规则,可选择SDONE和EOC用于触发。但使用EOC将使每通道采样时间至~1.4μs,这是因为触发信号上升沿时刻和SAR开始采样之间存在开销。SAR需要至少5个SARADC_CLK时钟来将DSI触发信号转换为信号采样开始。我们的设计要求更加苛刻。EOC信号与SARADC_CLK上升沿同步。在穿过DSI网络,并到达SAR的SOC(开始转换)之后,就已经略滞后于采样时钟的上升沿。因此,它需要6个SARADC_CLK时钟或大约340ns触发产生耗时。

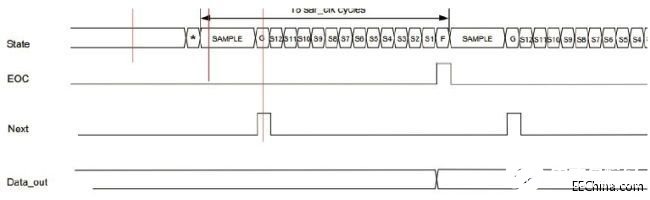

我们必须寻求另一种触发信号。幸运的是在SAR工作时,其可存储一个触发信号,但仅限一个,用于下一次扫描。因此我们可以使用SDONE触发转换。让触发产生耗时与SAR转换时间并行,SAR就可在当前转换完成之前存储该触发事件。现在对16通道的采样我们能有1μs的转换时间(见图12中的SDONE周期)。

第2步:在每次采样周期结束时暂时停止触发信号生成

在每次采样周期结束时,我们需要暂时停止触发信号生成,否则持续不断的采样将使FIFO溢出。如图6的红色部分所示,在选择通道0时,需关闭同步的D触发器(DFF)以暂时停止触发器输出。而在FIFO被ISR清空后,则需使用0x7F重置Count7单元,从而重新启用DFF输出。同时,应使用固件触发的方式在新周期中开始第一通道的采样,如图8所示。

图8:SAR ADC时序。

FIFO控制

UDB可配置为8字节FIFO,用于存储来自DSI网络的数据。图9显示了配置数据通路的概览图。FIFO时钟将数据采样到FIFO。F0 Load和F1 Load负责启用或禁用FIFO。两个状态信号可提示FIFO Full事件。