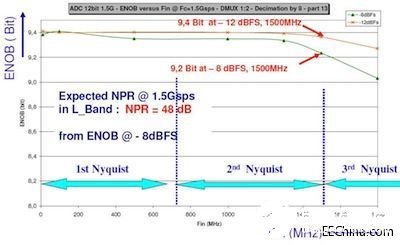

图3:EV12AS200的有效位数值。

ADC功能

鉴于多阵列设计是这种类型ADC的一种重要应用,ADC应该能够与阵列中的其它ADC匹配。因此增益、偏移和相位应具有调整功能。例如,下面描述的功能是非常理想的:

ADC增益控制:精调(±5%),使用10位DAC(±0.5 LSB)

ADC偏移控制:精调(±5%),使用10位DAC(±0.5 LSB)

ADC采样延时调整:30ps精调范围,10位DAC:30fs步距

这些功能还能用来交替多个12位ADC(用于增加实际采样率)。另外,在初始化过程中对齐多个通道的同步功能也很重要。这个功能还可以与触发功能共享,允许外部数字输入与模拟数据实现时间上的同步。

由于输出数据速率将接近内部FPGA的极限,一个重要功能是要能解复用(DMUX)这个数据,以引入更多输出端口的代价来降低数据速度。(EV12AS200提供1:2 DMUX解决方案)

另外一个重要功能是输入电压满刻度范围。ADC的谐波性能非常低,以致于输入驱动器上不良的杂散电平会严重影响系统性能。如果ADC能够接受低的输入电压,那么这个问题就能得以减轻。EV12AS200的输入电压范围是500mVpp。

设计考虑

时钟源和驱动系统的选择很重要,因为抖动是计算总噪声的一个主要因素。要想取得最优性能,100fs左右的抖动是比较理想的。这意味着源相位噪声为150dBc/Hz或以下,任何时钟缓冲器的附加抖动要远小于100fs。

PCB跟踪也是关键点,模拟跟踪应与源(或负载)匹配,才能取得接近1的VSWR。数字跟踪应匹配到100Ω阻抗,长度也要匹配到好于±2.5mm,以确保接口FPGA的摆率偏差不会太大。FPGA接口也是系统的一个复杂部分。为了实现高数据速率,可能需要扩展应用内部的串行/解串(SERDES)单元。

系统性能

系统性能可以通过后处理和实时技术进一步增强,比如积分非线性(INL)校正和使用高频振动(Dither)改善SFDR。

INL曲线形状对ADC的谐波性能有很大的影响。通过表征这个INL并使用接口FPGA中的查找表(LUT)可以最大限度地减小INL,从而提升SFDR性能。查找表校正是一种简单的减去或增加测量编码得到的INL值。使用这种技术对FPGA的规模影响很小,对吞吐量没有影响。在许多情况下,增加用于INL校正的查找表可以提高SFDR性能10dB。

向输入数据中增加带外噪声源也能改善SFDR性能。这可以是简单的一个经过低通滤波后的噪声发生器,通过使用多端口变压器将它增加到输入信号中。效果是在ADC输入范围内移动输入信号,有利于减少INL效应,并提高SFDR(见图4)。