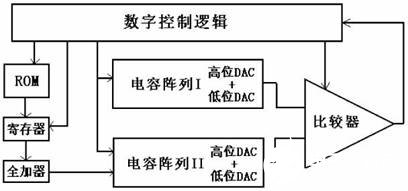

图3 数字校准算法示意图

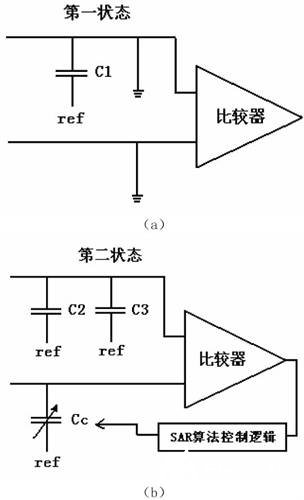

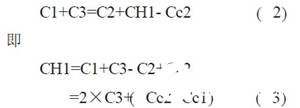

校准码的产生和使用可以有不同的算法, 中介绍了一种由高位到低位校准方法, 本文设计了一种由低位到高位依次校准的方法。校准测试时电容阵列工作于两种状态: 首先是接入一组电容, 电容阵列输出接地, 即比较器两输入端均为0, 如图4( a) 所示; 而后接入待测电容, 输出直接接入比较器两输入端产生比较结果, 如图4( b) 所示, 根据比较器的输出及外部的搜索算法调整电容阵列II 低位DAC 的输出从而测得待测电容所对应的寄生参数( 设计要求此DAC 的精度比正常使用时的DAC 至少高1位) , 通过对此数据的处理便可以得到相应的校准码。为实现由低至高的校准, 测试时需要用到电容阵列I 低位的3 组电容C1, C2, C3, 理想情况下它们的权值应与两组电容阵列低位DAC 的最高位相当,考虑到不匹配问题, 可设C1≈C2≈C3, 设电容阵列II 低位DAC 接入的电容值为Cc, 根据二进制加权电容阵列性质可知Cc 的等效输出范围在0 到2 倍C1 之间。初次测试时, 第一状态仅接入C1, 第二状态接到C2, C3 上, 同时电容阵列II 的可变Cc 接入,如图4, 通过观察比较器的输出, 可知, 当比较器输出跳变时, 有:

![]()

Cc1 为Cc 当前值, 可通过外部SAR 算法搜索得到。

图4 ADC校准时分为两个状态

接下来即可对高位DAC 的最低位进行测试和校准, 设此位电容权值为CH1, 第一状态电容接入C1, C3, 第二状态则接入C2, CH1 和Cc, 同理可得:

依上述方法可以推得:

![]()

ΣΔCc 为每位所对应Cc 差值与已校准低位Cc 差值的累加和, 将此电容值对应的二进制码用有符号数表示即所需校准码, 随后可以通过一次性烧写电路存储到ROM中, 完成SARADC 的校准测试。

数字校准的具体实现方法, 可通过添加芯片状态控制端口实现。如表1 中所示, 测试时将两个控制端口接地, 应用上述算法获得校准码; 随后将控制端口P2 接至高电平, 此时将所需的校准码写入到芯片的ROM中; ADC 正常使用时, 将两个控制端口接到数字电源上即可。各个工作状态的具体逻辑电路实现, 遵循数字集成电路设计规程, 并需针对不同状态对芯片的端口进行配置。