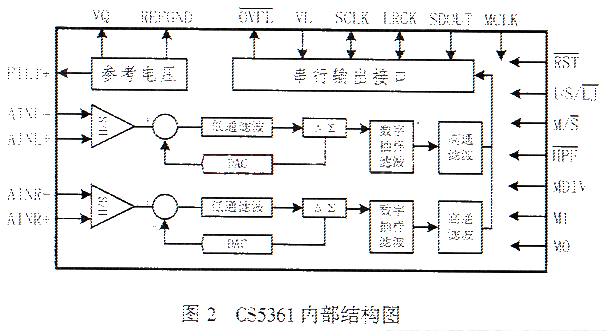

M0、M1:操作模式选择端;

OVFL:左右通道溢出指示脚;

AINL+,AINL-,AINR+,AINR-:分别为左右通道模拟信号的+、-输入端;

VA:+5V模拟电源输入端;

VQ:内部静态参考电压,使用时应连接滤波器;

REFGND:内部采样电路参考地;

FILT+:内部采样电路参考电压。

3 基本工作原理

CS5361转换器工作时,应根据工作的具体需要确定工作模式、操作模式、输出格式、高通滤波模式等工作参数,下面分别介绍这些参数的意义及设置方式。

3.1 操作模式及采样率范围选择

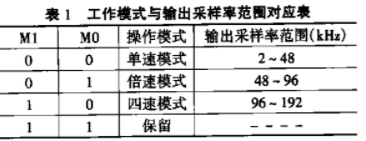

CS5361转换器的M1、M0引脚状态可用于决定芯片的操作模式,通过设置适当的操作模式,可使CS5361的输出采样率(FS)在2kHz到192kHz之间进行选择。每种操作模式对应的采样率范围如表1所列。

对于每种操作模式,芯片的性能可能略有差异,例如,工作在单速模式时,CS5361的数字滤波器的通带为0~0.47FS,阻带大于0.58FS,阻带衰减优于95dB,滤波器群延时为12/FS(S);工作在倍速模式时,CS5361的数字滤波器的通带为0~0.45FS,阻带大于0.68FS,阻带衰减优于92dB,滤波器群延时为9/FS(S);工作在四速模式时,CS5361的数字滤波器的通带为0~0.24FS,阻带大于0.78FS,阻带衰减优于97dB,滤波器群延时为5/FS(S),因此,应根据实际需要适当选择CS5361的操作模式。

3.2 系统时钟MCLK和MDIV状态

当CS5361的操作模式确定后,系统时钟和MDIV的状态将决定具体的输出采样率(FS)、左右通道时钟LRCK和串行移数时钟频率(SCLK)。

对于单速模式,其采样率范围为2~48kHz,因此,当MDIV为0时, MCLK的范围应为512kHz~12288kHz;而当MDIV为1时, MCLK的范围应为1024kHz~24576kHz;

对于倍速模式,采样率范围为48~96kHz,故在MDIV为0时, MCLK的范围应为6144kHz~12288kHz;为1时MCLK的范围应为12288kHz~24576kHz;

对于四速模式,由于其采样率范围为96~192kHz因此,当MDIV为0时,MCLK的范围应为6144 kHz~12288kHz;而当MDIV为1时, MCLK的范围则应为12288kHz~24576kHz。

3.3 主从模式设置

通过设置芯片的第2脚为高电平可使CS5361进入主模式,反之进入从模式。主从模式的区别在于进入主模式时,LRCK、SCLK为输出信号?而在从模式时,LRCK、SCLK为输入信号,并应保证LRCK、SCLK与MCLK同步,同时应使LRCK=FS、SCLK=64FS,否则将影响器件性能的发挥。设计主从模式的目的在于,多片ADC同步工作时,可以使其中的一片工作于主模式,其它工作于从模式,从模式ADC的LRCK、SCLK来自于主模式的ADC,这样可保证多片ADC的同步工作。