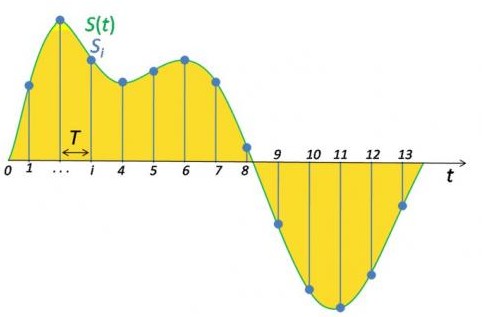

由于实际的 ADC 不能进行瞬时转换,因此在转换器执行转换期间(称为转换时间)输入值必须保持恒定。一个被称为采样保持电路——在大多数情况下,它使用一个电容来存储输入端的模拟电压,并使用一个电子开关或栅极来断开电容与输入端的连接。许多 ADC 集成电路包括内部的采样保持电路模块。图中的 T 为采样周期,其倒数就是采样频率。

混叠

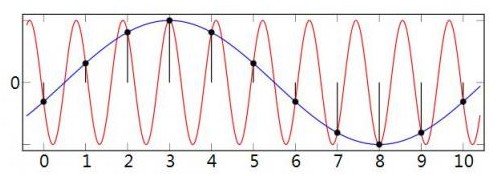

ADC 通过在不连续时间间隔(离散的含义)内对输入值进行采样来工作。假设以高于奈奎斯特速率的频率对输入进行采样(定义为有用信号频率的两倍),则可以重构信号中的所有频率。如果对高于奈奎斯特速率一半的频率进行采样,则会将它们错误地检测为较低频率,这一过程称为混叠。之所以会出现混淆,是因为每个周期对函数进行两次或两次以下的瞬时采样会导致丢失周期,从而出现频率错误地降低的情况。例如,以 1.5 kHz 采样的 2 kHz 正弦波将重构为 500 Hz 正弦波。

为了避免混叠,ADC 的输入必须经过硬件低通滤波,最简单的实现形式为一阶无源 RC 滤波网络,以去除采样率一半以上的频率。这种滤波器被称为抗混叠滤波器,它对于实际的 ADC 系统至关重要,该系统适用于具有更高频率内容的模拟信号。在需要防止混叠的应用程序中,可以使用过采样来大大减少甚至消除混叠。

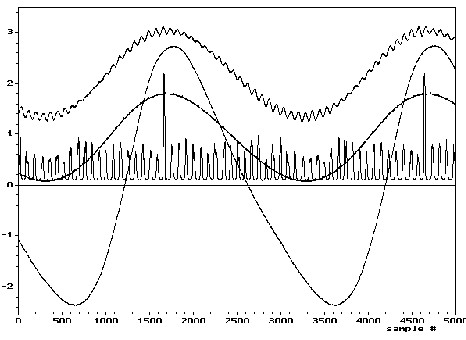

例如:六种不同采样速率采集的数字序列重建的 4 种波形。其中两种波形在采样率足够情况下未出现混叠。另外两个说明了在较低速率下会失真(混叠增加)。

过采样

为了经济起见,通常以所需的最小速率对信号进行采样,结果是引入的量化误差是 白噪声在转换器整个通带上的扩散。如果以远高于奈奎斯特速率的速率采样信号,然后进行数字滤波以将其限制为信号带宽,则会产生以下优点:

过采样可以更轻松地实现模拟抗混叠滤波器

降低的噪声,尤其是在过采样之外还采用噪声整形处理后。

白噪声长啥样?