2 关键电路设计

2.1 采样保持电路

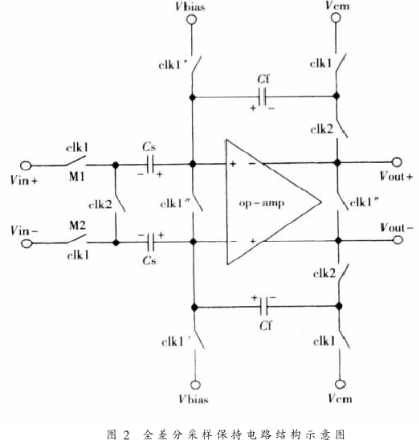

采样保持电路是流水线ADC中关键的模块。它在采样周期时,对输入的模拟信号进行准确采样,在保持周期时,将采样结果保持一段时间,即实现模拟信号的离散化,其速度和精度直接决定了整个流水线ADC的速度与精度。本设计中采用了全差分结构底极板采样电荷转移结构采样保持电路,其结构示意图如图2所示。该电路使用两相非交叠时钟,除了时钟clk1之外,还存在时钟clk1′和clk1″,按照clk1′、clk1″和clk1的顺序依次闭合,然后再相继断开。

根据时钟,该电路的工作可分为采样和保持两个阶段。在采样阶段,时钟clk1、clk1′和clk1″有效,运算放大器的两个输入端被短路,电容CS对输入信号进行采样并以电荷的形式存储起来。在保持阶段,clk2有效,存储于CS上的电荷转移到电容Cf上,从而实现了对采样电压的保持。由于采用了全差分结构、相应的时钟控制以及底极板采样技术,可以有效地降低开关沟道电荷注入、时钟馈通、共模电压、温度漂移等的影响,提高了电路的精度。此外为了减小由输入采样开关M1、M2的非线性导通电阻引入的非线性,还采用了栅压自举电压控制的NMOS采样开关以改进采样开关的线性度,提高精度及输入信号的范围。

2.2 运算放大器

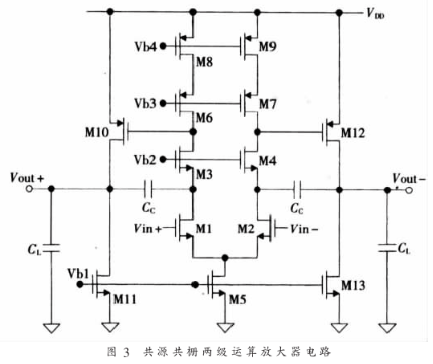

运算放大器是采样保持电路的核心,其性能直接影响采样保持电路的速度和精度,是流水线ADC电路设计的关键。本设计采用共源共栅两级运算放大器[4],其第一级采用高速的套筒式共源共栅运算放大器来弥补两级运算放大器速度慢的缺点,因此整个电路具有相对较高的增益、较高的速度、较低的功耗和噪声及较大的输出摆幅等特点,其电路结构如图3所示。

由于在第一级中采用了共源共栅(cascode)结构,极大地提高了第一级的输出阻抗,具有较高的增益。其直流增益可表示为:

![]()

在设计中采用了共源共栅补偿,即在第一级的cascode结点和第二级的输出结点之间接了一个补偿电容CC。这种补偿产生了一个低频主极点,并在较高频率处产生了两个互补的零点和极点。这种补偿方法同Miller补偿相比,在提高相位裕度的同时,可以提供更大的带宽。补偿电容CC的大小对于运算放大器的相位裕度和单位增益带宽都有很大的影响,并且随着CC的增加,运算放大器的单位增益带宽会降低,而相位裕度则会增大。