仿真结果表明,该运算放大器在3.3V的电源电压下,直流增益为98dB,单位增益带宽为348MHz,相位裕度位为61度,完全能够满足系统的要求。

2.3 动态比较器

在流水线ADC中,每一级内部的子ADC都是一个由多个比较器组成的全并行ADC,可以说比较器是整个ADC中使用最多的单元电路,其功耗是整个ADC功耗的一个重要组成部分。由于采用了数字校正技术,可以对比较器的输出信号进行校正,因而对比较器的失调指标要求比较宽松,使得在比较器的设计中,在满足速度要求的前提下,可以通过牺牲精度来降低功耗。本设计中采用差分结构动态比较器[5],它由交叉耦合的差分对和锁存器负载组成,由于整个比较器电路的电源和地之间不存在直流通路,因此不消耗静态电流,其结构如图4所示。

当Vlatch信号为低电平时,M5、M6管截止,M9、M12管导通,比较器的两个输出端全部被置位为高电平,此时,M7、M8管导通,M1~M4管的漏端被充电至(VDD-VT),而M5、M6管的漏端电压则由比较器的输入信号决定。当Vlatch信号为高电平时,M9、M12管截止,M5、M6导通,差分对开始工作,对(Vin+-Vin-)和(Vref+-Vref-)进行比较,引起比较器左右两个支路也即两个输出端的泄放电流不同,从而导致锁存器发生翻转,输出比较结果,同时电源电流也被切断。

由上面的分析可以看出,在整个比较过程中,功率消耗仅仅发生在转换瞬间,其静态功耗可以忽略不计;同时该比较器的输入管在比较开始时工作在饱和区,具有较大的跨导,因此这种差分结构的动态比较器具有较高的速度和分辨率。仿真结果表明,该比较器在不同的仿真条件下失调电压小于15mV,建立时间约为3ns,而功耗仅为0.2mW。

3 仿真结果与结论

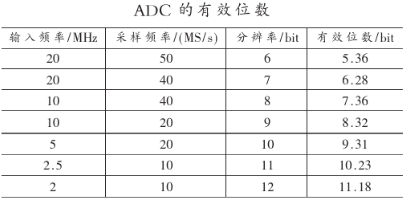

本文基于0.18μm CMOS数模混合工艺模型,使用Hspice对流水线可重构ADC中的关键电路进行了仿真,并使用Matlab对整个可重构流水线ADC进行了行为级仿真。表1总结了在不同的重构控制配置信号下,即在不同采样频率和分辨率位数下,可重构流水线ADC的有效位数。从表1可以看出,所设计的可重构流水线ADC在给定的采样频率和分辨率位数下,都达到了设计要求。

本文在传统流水线结构模数转换器基础之上增加了一个重构配置控制电路及其他部分电路,设计了一种可重构流水线结构模数转换器。该模数转换器可以根据输入信号范围及系统需要通过一个重构配置控制信号来动态地配置采样频率的大小及分辨率的位数,特别适用于多标准收发器中。在实际应用中,根据输入信号的频率范围及系统需要,可以通过重构配置控制信号来配置ADC的采样频率和分辨率位数。