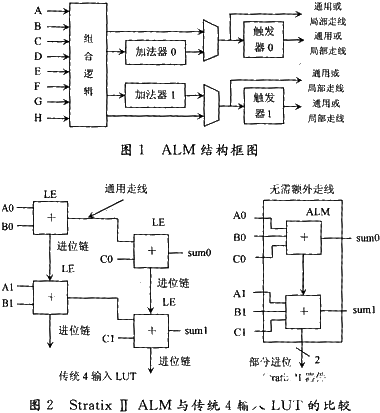

图2列出了和传统的4输入LUT结构的FPGA相比较,采用ALM的StratixⅡFPGA器件例化3输入加法器的优势。从图2中可以清楚地看出,对于同样3个2 b数据相加的逻辑结构,传统4输入LUT结构的FPGA例化需2级完成,占用4个LE,而对于采用ALM的StratixⅡFPGA器件来例化,只需一个ALM即可。

2 、针对ALM的加法树设计

目前大多数FPGA都是基于传统的4输入LUT加上一个触发器的LE结构,如Altera的Stratix,APEX,Cy-clone和FLEX10K等器件族。他们在实现加法树时只能采用2输入加法树,而采用ALM结构的StratixⅡ器件实现加法树时,可根据需要采用3输入加法树或2输入加法树。这样,就能压缩加法树总的步骤数,提高加法树的性能。减少的加法树步骤n可由以下公式计算出:

![]()

这里N是指输入数据的数目。

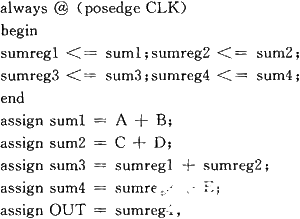

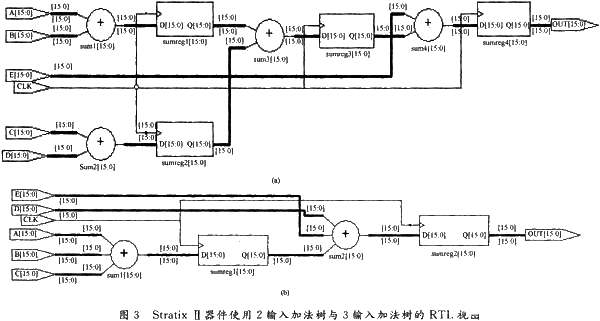

对于传统的FPGA,如果实现A+B+C三个数的加法器,最高频率的方法是先实现2个数的加法,如A+B,将和用寄存器打一拍,然后将寄存器的和与第三个被加数(C)相加。这种方法实现1比特加法器时,A+B相加将使用1个加法器和1个寄存器,即一个LE,需1级逻辑完成。这种思路通常被称为2输入加法树结构,将加法树逐级拓展,可以实现更长的加法树结构。如果实现A+B+C+D+E五个数(16位)的加法树,使用这种2输入加法树方法共需3级寄存器缓存。其Verilog程序主要算法如下给出,选用器件StratixⅡEP2S15FC484-5,图3(a)给出了经过Synplify Pro 7.7综合后的RTL视图。综合结果为:默认约束条件下,共需64个ALM,实现估算的时钟频率为400.00 MHz。

由于ALM对输入可以在3到7之间自由配置,那么对于上述16比特的5个数的加数求和的加法器,可以让ALM配置成6输入的LUT,使用6-LUT可以同时完成3比特加法,用2个3输入的加法器取代上述的4个2输人加法器来实现。其算法如下给出,在其他同样条件下,综合后的RTL视图如图3(b)所示,综合结果为共需32个ALM,实现估算的时钟频率为427.30 MHz。可见节约了50%的ALM资源。