采集系统设计

系统分析及芯片选择

首先确定系统要求。目前标准规定的VGA分辨率从640×480-1280×1024之间可调,刷新率为60-80Hz可调。系统应能接受最高情况为分辨率1280×1024,刷新率60Hz。在这种情况下,图像像素点频率为:1280×1024×60=75MHz。

VGA是用于给显示器等模拟设备提供图像信号的模拟接口。它有RGB3个模拟信号分量以及行场同步信号,其中行场同步信号是符合TTL电平的脉冲信号。由于模拟的VGA信号中包含有场同步时间和行同步时间及消隐时间,因此当图像为1280×1024@60Hz的情况下,AD转换后像素点频率要比实际算出来的75MHz还高。这么高的采样率对于AD提出了很高的要求。因此采用Analog Device公司的芯片。AD芯片具有3路采样精度为8bit的通道,最高采样率为140MSPS,具有300M的模拟带宽,并且专门对计算机及工作站图像接口进行了优化,最高可满足对分辨率为1280×1024,刷新率为75Hz的视频进行采样。

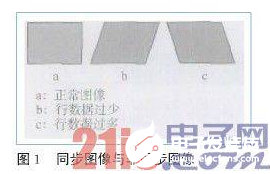

由于AD的采样率比较高,相应的输出数据率很也高。在系统要求的最高情况下,象素点频率为108MHz,相应的数据率为324Mbit/s(RGB3个分量,每个分量8bit)。同时,由于采集的是图像数据,因此系统对行同步要求比较高,因为如果在某一行的图像数据中丢失了某一个或多个点的数据,整个图像就会产生倾斜,如图1所示。图a为正确采集后得图像,没有发生倾斜;图b为行采集数据小于显示的水平分辨率;图c为行采集数据大于显示的水平分辨率。因此需要对每行的数据进行突发存储,保证数据不丢失。突发的长度为图像的水平分辨率。

从上面的分析可知,AD后数据的及时存储要求很高,在极端条件下系统必须以110MHz左右的频率进行突发长度为1280×3Byte的存储。传统的通过DSP把数据存储到SDRAM的方法不能满足这么高的速度和这么长的突发长度。因此我们采用FPGA直接控制SDRAM存储的方式进行。考虑到图像数据的频率和大小,我们采用工作在133MHz的SDRAM。

由于原始的图像数据量很大,需要占用比较大的存储空间,因此对采集到的图像数据还要进行后续处理。所以FPGA除了接收AD转换后的数据和控制SDRAM之外,还需要为图像的后续处理提供接口。

综上所述FPGA需要实现如下功能:同步接收AD采集的数据;读写SDRAM;提供后续图像处理接口;提供控制接口。

设计中采用Altera公司Cyclone系列的FPGA EP1C6。EP1C6具有2个锁相环,包含5980个逻辑单元,相当于12万门的规模,同时还包含了最高频率200MHz,92160bit的内部RAM。该芯片的频率和引脚IO等资源都能很好的满足本系统的要求。