总体设计

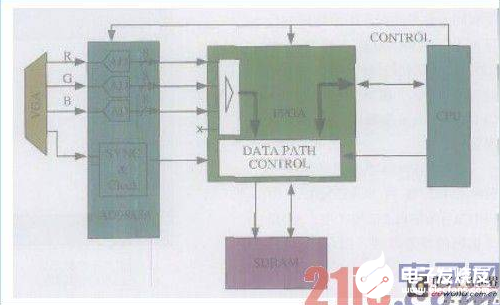

采集系统总体框图如图2所示。

采集系统由AD、FPGA、SDRAM和主CPU组成。整个系统由CPU控制。进行采集时,首先CPU根据行场同步信号判断图像的分辨率和刷新率,并对AD和FPGA进行相应的设置。其次,CPU使能FPGA进行采集。待采集一帧结束后,CPU即可对图像数据进行处理。

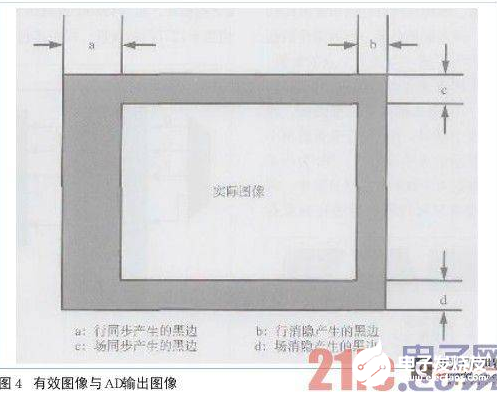

AD模块能够采集多种VGA图像格式,但却不能自动检测图像格式,必须通过它提供的IIC接口进行设置,我们在主CPU中实现对图像格式的自动检测,并对AD模块进行设置,另外,不同格式的VGA图像中场同步信号的有效脉冲电平没有统一,AD模块可以对输入的场同步信号极性进行自动检测并表示在内部寄存器中,通过读取该寄存器可以判断输入VGA信号场同步的极性。AD模块输出的场同步信号可以实现对输入场同步信号的反相。FPGA内部的同步逻辑只支持一种有效电平的场同步信号,因此在采集前需要通过读取AD内部的寄存器判断当前输入同步信号的极性,以确定是否需要设置AD芯片对场同步信号进行反相处理。

为了方便主CPU对FPGA的控制,FPGA提供了IIC接口。主CPU可以通过与AD模块一样的IIC接口控制FPGA。设置采集图像的大小,图像存储起始地址,消隐时间长短等信息,从而保证采集图像大小精确、完整,同时为了方便主CPU对图像进行后续的处理,FPGA把存储图像的SDRAM转换成ASRAM接口提供给CPU处理,从而把存储图像的空间直接映射到了CPU的寻址空间。CPU可以通过DMA快速的对图像数据进行读取和处理,提高系统效率。

FPGA内部设计

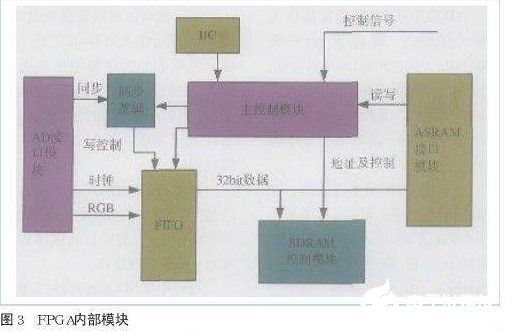

FPGA内部模块如图3所示。

FPGA内部由主控制、SDRAM控制器、AD接口、FIFO、ASRAM接口、IIC等模块组成。主控制模块负责接收CPU的控制信号和协调各个模块之间的工作,SDRAM控制模块实现对SDRAM的操作逻辑。AD接口模块接收AD模块输出的数据和同步信号并保证图像数据的行场同步,ASRAM接口模块转换CPU对ASRAM的操作为对SDRAM的操作指令,IIC逻辑模块接收CPU对FPGA采集系统的各种参数设置和控制。[page]

系统FPGA主要时钟频率有SDRAM工作频率133MHz,由EP1C6自带的PLL倍频产生;AD模块输出的像素时钟,由AD芯片内部PLL产生,IIC模块中的时钟,由CPU产生。其中AD芯片输出的时钟根据不同的输入图像格式有比较大的变动范围,从25-108MHz,而SDRAM的读写时钟固定为133MHz。因此在这两个不同频率的时钟之间必须加FIFO来同步,FIFO使用QuartusII软件中提供的免费IP核,通过使用FPGA内部高速RAM来实现。