AD模块负责与AD芯片的接口逻辑。前面已经分析了图像采集中同步的重要性,如果图像中的某一行数据不完整,那么将影响到整个图像。AD模块通过AD芯片输出的行场同步信号来实现图像数据的同步,以AD芯片输出点频作为FIFO模块的写时钟,行场同步信号的组合逻辑组成FIFO的写使能。另外,由于模拟的VGA接口存在有行、场同步时间和行、场消隐时间,为了保证图像采集的精度和完整,AD芯片要求把点频设置为比实际有效点频大20%-30%,因为在AD转换后的图像中行幅和场幅往往比实际图像大,造成图像有比较大的黑边。如图4所示。为了获得准确的图像数据,AD模块设置了计数器可以过滤图像起始的黑边。其计数值可以通过IIC接口进行设置。

SDRAM有多种不同长度的突发模式。在本设计中由于AD输出的频率最高接近110MHz,突发存储的长度比较长,为了能保证数据能够及时存储,工作频率为133MHz的SDRAM必须工作在整页突发的模式,以达到最高的数据吞吐率。

为了提高通用性,本设计中把SDRAM接口转换成ASRAM接口提供给主CPU,避免了SDRAM工作频率和CPU外部时钟不同时造成的SDRAM控制权切换的麻烦,提高对各种CPU的兼容性。ASRAM接口逻辑实现对CPU地址到SDRAM地址的映射及操作时序的转换。主控制模块产生相应的SDRAM控制指令,控制SDRAM读写。SDRAM的操作对于CPU来说是透明的。

该采集系统也可对4路8bit的AD通道进行采集,因为FPGA内部的AD逻辑模块提供了32bit的接口,VGA采集方式只用了其中24bit。采用4路8bit模式时只需把前端AD部分做一些调整。

实际应用

在中国船级社对船载航行数据记录仪的性能要求中,要求船载航行数据记录仪应能连接到欲记录其图像的雷达显示器的视频缓存输出,通过专用的雷达缓存输出接口,数据记录仪需记录一系列单个和整屏的视频帧。该要求设计的显示器的分辨率应在640×350到1280×1024之间,刷新率在60-85Hz之间。采用本设计可以完整实现该要求。

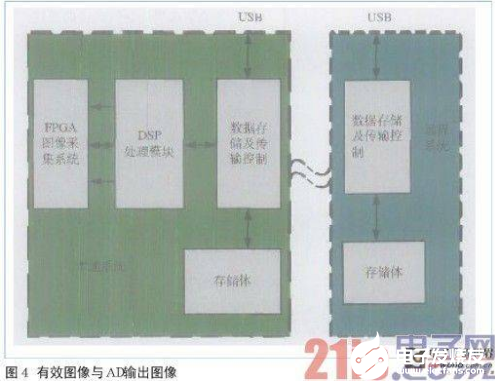

图5所示为完整的雷达图像记录系统框图。

总体上系统由本地端系统和远程系统两大部分组成。本地端负责对雷达图像的采集压缩和存储备份。远程系统保存雷达图像的副本。本地系统由采集、处理、存储传输3大部分组成。采集部分就是前文所述的以FPGA为核心的雷达图像采集系统。处理部分采用TI公司C6000系列DSP作为系统的CPU。存储传输部分主芯片则采用了Samsung公司的SOC芯片S3C2410。存储体则采用了多片大容量的NAND Flash。