今天小编要和大家分享的是布线技巧与EMC相关信息,接下来我将从普通点对点布线的缺点,实际上,关于水电改造时电线的布线,素来有 \这几个方面来介绍。

布线技巧与EMC相关技术文章普通点对点布线的缺点

最近,硅谷有一定著名的公司,我们称之为NEWCO公司,曾经制造了他们的第一台调整处理机的巨大原型机。他们决定使用点对点布线,以避免制作印刷电路板的费用和时间。原型机是在16IN/20IN的电路板上通过导线绕接技术而构建的。这一个原型机包含600多个门电路和2000个不同的信号网络。下面是有关信号网络的一些计数据:

网络的数目:2000网络的平均长度:40IN(未端接的)引线在接地平面上方的平均高度:0.2IN线径(AWG30):0.01IN直径信号上升时间:2.0NS转折频率:250MHZ(=0.5/2.0NS)

1、点对点布线的信号畸变

在NEWCO的设计中,上升时间为2.0NS,其电气长度为:

区分集总系统和分布系统的临界尺寸是:1/6=3.9IN

NEWCO认为,因为导线的平均长度基本上在这一界限之内,所以电路只会有很少的振铃。但是他们错了。

NEWCO认识到,当电路大于1/6时,将表现分布状态,他们知道,分布电路如果不端接,就会振铃。因为他们的电路是集总的,所以错误地认为不会振铃。

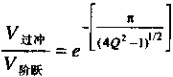

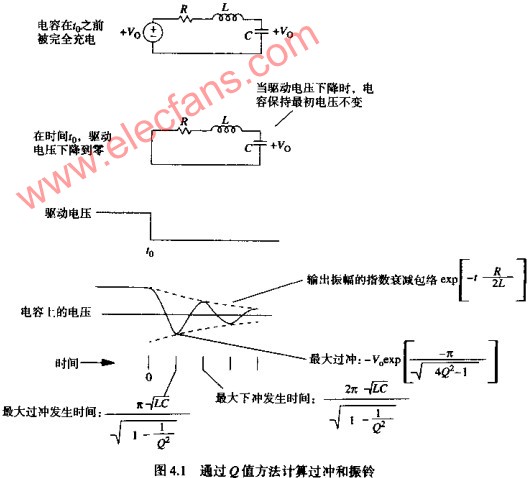

集总参数电路可能振铃,也可能不振铃,这取决于电路的Q值。电路的Q值显示出电路中信号衰减消逝的快慢。在低Q值电路中,信号衰减得很快,而在高Q值电路中,信号却来回振荡,经过几个振铃周期后才慢慢地消逝。Q值在技术上被定义为总存储能量与每个振荡周期所衰耗能量之比。从这个定义引出一个近似公式,将特定电路的最大过冲电压用Q值的一个函数来表示:

其中,V过冲=超出稳态输出电平的输出上升量,V V阶跃=预期的稳态电平,V Q=谐振参数(这里假设﹥0.5)

图4.1中的理想二阶电路以时间常数2L/R衰减,完全符合上式。

根据经验,在一个理想阶跃的输入响应中,Q值为1的数字电路显示出16%的过冲,Q值为2的数字电路则显示出44%的过冲。任何Q值低于1/2的电路都不会过冲或振铃。一个电路上产生的振铃是电路本身的固有谐振频率和驱动器上升时间之间关系的一个函数。我们也将研究这个问题。

一旦我们知道了电路的电感,计算一个数字电路的Q值是很容易的。这提示我们关注点对点布线的基本问题:高电感。

当一个高电感引线工作于大电容负载的情况下时,会形成一个高Q值的电路。

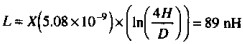

我们可以采用附录C中列出的关于一个位于接地平面之上的圆柱体导线计算公式,来算出NEWCO系统中一个典型网络的电感L:

其中:L=回路电感,H D=绕接线的直径,0.01IN H=线路在接地平面上的高度,0.2IN X=线的长度,4IN

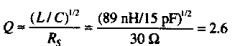

采用式( ),可以计算出由驱动的源端电阻、导线的串联电感和接收器的负载电容组成的RLC电路的Q值:

),可以计算出由驱动的源端电阻、导线的串联电感和接收器的负载电容组成的RLC电路的Q值:

R=30欧(一个TTL驱动器的输出电阻)L=89NH(平均接线电感)C=15PF(典型负载)

Q值为2.6意味着,对于一个理想的阶跃输入,将得到不小的振铃。由式(),预期最坏情况的过冲电压为:

V阶跃=3.7V(TTL阶跃输出)Q=2.6(来自上式)

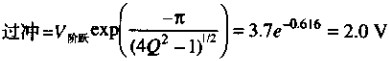

只有当NEWCO的逻辑驱动器在振铃频率以上传输有效能量时,这个最坏情况的过冲才会发生。采用下式可以找出振铃频率:

频谱宽度的衡量标准是转折频率,按照式()的定义,NEWCO的逻辑门电路转折频率(250MHZ)远远高于振铃频率(138MHZ),因而存在大量的电能,可以引起振铃过程。转折频率如果正好等于138MHZ,振铃就将减小大约一半。转折频率更低的逻辑门电路产生的振铃还会更小。

如果完全在时域中考虑,我们可以断定,当上升时间等于振铃周期的一半时,最坏情况下的振铃被减少一半。上升时间越长,引起的振铃越小。相反,当上升时间远远小于振铃周期的一半时,将引起最坏情况下的振铃。

我们可以从Q值分析中发现更多的论据。我们知道,NEWCO的电路一般在138MHZ频率振铃,最大过冲为2.0V。根据线性电路理论可以知道,最坏的过冲总是发生在阶跃边沿后振铃周期的二分之一处,因此,能预知最大过冲将会发生在每个逻辑转换后的3.6NS处。

2、点对点布线的EMI

EMI代表电磁干扰。开放电流的环路,比如在导线绕接产品中,将会立刻被标上大大的戏色EMI警示。传输快速变化电流的大电流环路会产生瞬变的磁场。来自这些环路的磁场直接辐射到FCC技术人员的检测天线中,他们将拒绝给你的数字产品颁发合格证明。

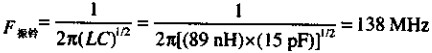

传输线极大地减少了EMI。它通过限制信号返回电流的流动路径来达到这一目的。对于普通的导线,电流从一个逻辑驱动器的信号线流出,然后以某种方式沿着电源返回。这两个路径之间的距离,或者说它们之间的总环路面积,也许是几个平方英寸。依照FCC测试规程,由此而产生的磁场直接与信号电流环路的总面积成正比。

传输线结构保证了信号返回电流紧贴着信号输出路径。产生的实现电流环路面积非常小,由输出和返回电流路径产生的磁场相互抵消,极大地减少了EMI问题。

参考图4.2,一个印刷电路板上的信号走线位于完整接地平面上方0.005IN处,其电流环路面积比位于接地平而上方0.2IN的开放导线小40倍。对于相同的信号上升时间,这样一个印刷电路板的每条走线辐射的电磁能量比NEWCO原型机的每条导线小32DB。

3、点对点布线中的串扰

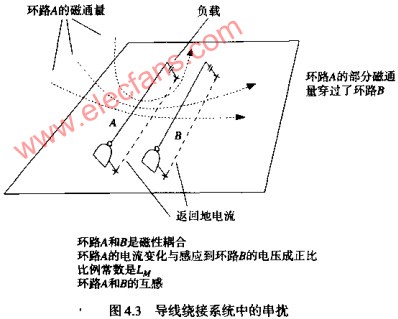

如图4.3所示,由于变化磁场的作用而产生串扰。由流经环路A的电流产生的一些磁力线穿过了环路B。因此,环路A中的电流变化改变了由环路B所包围的磁能量。环路B中磁能量的变化感应产生了环路B上的噪声电压,称为串扰。环路A的电流变化与环路B的电压成比例,其比例常数称为环路A和B之间的互感,用符号LM表示。

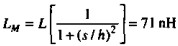

在调整条件下的导线绕接系统中,患扰是一个主要的问题。让我们来计算NEWCO会有多大的串扰。假设有两个相邻的环路,每个4IN长。0.2IN高,平行间距0.1IN。

可以用上式中的电感值作为传输导线的电感。

H=0.2(距地平面的高度)S=0.1(两线之间的距离)L=89NH(一条导线的电感)

其中,LM=两线之间的互感

这一数值与单个网络的自感相当。这就是说,两个网络将会高度地耦合,预计会出现大量的串扰。

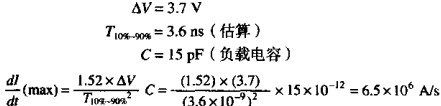

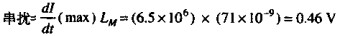

串扰计算的下一步是找出驱动环路的最大DI/DT,并乘互感值得到串扰电压值。在此,我们最好的推测是负载电容上接收信号的实际上升时间是3.6NS(这是最大过冲所需的时间)。把这个数值代入到下式:

计算得出串扰为12%(0.46V)

你感到惊讶吗?仅4IN的相邻导线就产生了460MV的串扰。在0.1IN的半径内,一个好的技术人员能轻易地将10或20根导线绑在一起。来自每根导线的串扰会线性地叠加。来自10根邻近导线的串扰将达到50%,足以引起严重的差错。

在构造高速总线时,采用大捆的平行导线从一处连到另一处的做法是很可怕的,技术人员为了能看到清楚写在每个芯片背面的引脚号,他们喜欢把芯片之间的导线归扰到一起,这个习惯使串扰问题更加恶化。直接的对点对点边线,把导线下压,以尽可能地贴近接地平面,比集中或捆绑导线要好得多。

当项目终止的时候,NEWCO放弃了它的原型机,甚至从来没有让它完全运行过来,他们浪费了好几个星期的宝贵设计时间,而且没能在印刷电路布局之前验证设计中的关键问题。

关于布线技巧与EMC就介绍完了,您有什么想法可以联系小编。