今天小编要和大家分享的是接口,总线,驱动相关信息,接下来我将从基于PXI总线接口的高速数字化仪模块设计实现方法概述,thinkpade420 1141aa6左侧/vga接口图片这几个方面来介绍。

接口,总线,驱动相关技术文章基于PXI总线接口的高速数字化仪模块设计实现方法概述

PXI总线是NI公司在计算机外设总线PCI的基础上实现的新一代仪器总线,已经成为业界开放式总线的标准,基于PXI总线的数字化仪模块是现代测 试系统中重要的一种数据记录与处理设备。设计一个双通道12 bit/250 MHz采样频率的高速数字化仪模块,以高性能FPGA器件为核心,实现对高速A/D的控制以及高速数据处理和存储,解决了长时间高速记录信号的测试难题。

1 系统工作原理

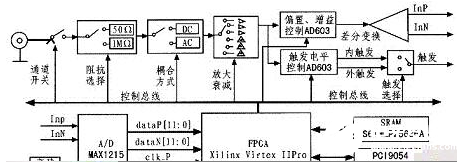

数字化仪模块主要由前端信号调理通路、模数转换电路、数据存储单元、数据采集控制电路、PXI接口电路等部分组成,其原理框图如图l所示。

高速模拟信号首先经过信号调理通路进行放大、衰减等处理,将幅度调整到A/D转换器允 许输入的电压范围内,并转化成LVDS格式的差分信号,然后送到A/D转换器;FPGA芯片接收A/D输出的高速数据流,经过降速、抽取滤波等处理后,存 储到数据存储单元SRAM中,并发出中断信号,PXI主机响应中断后经由FPGA将存储在SRAM中的数据读入主机内存,完成后续的数据处理和显示。 PXI主机通过PXI总线发送控制命令,经FPGA译码后实现对数据采集和调理通路控制。该数字化仪模块为每个通道预留了4Mb的存储容量,当组成PXI 测试系统时,可以将数据写入计算机硬盘,实现更长时间的记录。两个通道可以独立工作,也可以相互关联。采集方式可以有内触发、外触发、软件触发、通道触发 等多种模式。

2 系统设计实现

2.1 模块化的FPGA设计

本文所设计的数字化仪是基于高性能FPGA芯片实现的,FPGA承担了绝大部分的控制和数据处理任务,是本设计的核心器件。对FPGA进行模块 化设计,是大型系统设计的常用方法。合理分割功能模块,能加快FPGA的开发,也有利于代码的移植和重复利用。在设计时将FPGA分成高速A/D接口模 块、数据降速模块、调理通路控制模块、存储接口模块、PXI接口控制模块等主要功能模块设计。FPGA内部模块划分和数据流向如图2所示。