今天小编要和大家分享的是接口,总线,驱动相关信息,接下来我将从基于CPCI总线接口和LVDS接口的接收和传输测试数据实验设计,cf曼陀罗潜伏者图片这几个方面来介绍。

接口,总线,驱动相关技术文章基于CPCI总线接口和LVDS接口的接收和传输测试数据实验设计

0 引言

随着科学技术的迅猛发展,越来越大的数据传输量和越来越高的数据传输速率成为信号处理系统亟待解决的问题。因而,开发一种能够实时处理大量高速数据,同时兼具稳定性和通用性的新总线成为整个数据链技术中迫切需要解决的瓶颈之一。CPCI (紧凑外围设备互联总线)结合了PCI总线的电气特性和欧式卡的机械标准,可提供132 MB/s的峰值带宽[1],同时CPCI构架开放,性能优良,在可靠性、兼容性和机械性能等方面均有优势。 因此,CPCI总线已成为当今应用最广泛的工业计算机总线,基于CPCI总线的工业控制计算机已经成为解决大量高速数据处理的一个新方向。

基于某测试任务,本文详细阐述了通过CPCI总线接口和LVDS接口接收和传输测试数据,在保证可靠性的前期下,提高了地面设备接收和处理数据的速度。测试结果表明,此方法可行可靠,圆满完成了测试任务。

1 总体设计

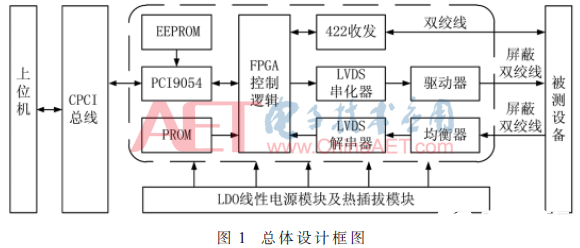

本设计的主要工作是对外接CPCI设备进行命令下发、状态检测及数据接收操作。其主要工作流程是:由上位机下发命令字控制整个系统的正常运行,主控芯片XC3S400通过PCI9054桥接从背板总线接收主机卡发出的命令字,完成逻辑控制;通过RS422接口与外接设备进行通信,控制外接设备进入相应的工作状态以及接收其相应的状态返回;通过LVDS接口接收外接设备的高速数据,将数据写入FPGA的FIFO后,由PCI9054通过DMA控制器将接收的数据回传至主机卡。总体设计框图如图1所示。

整个设计以FPGA为控制核心,充分利用其强大的可编程能力[2],能够灵活控制总线传输速率等多个指标,在增加系统通用性的同时,也充分发挥了CPCI总线高速传输的优势。

2 RS422接口设计

RS422接口用来下发命令字和接收状态字,由于信号码率较低,为625 kb/s,因此设计中主要考虑传输的稳定性和可靠性。本设计针对此问题首先选择了抗干扰性强的差分对信号传输数字量,同时对信号采取隔离措施,以防止前后级设备之间的互相干扰。接口电路示意图如图2所示。