今天小编要和大家分享的是接口,总线,驱动相关信息,接下来我将从数控振荡器的基本结构以及电路原理解析,组合逻辑电路如下图所示,1)写出输出函数f的表达式,2)这几个方面来介绍。

接口,总线,驱动相关技术文章数控振荡器的基本结构以及电路原理解析

1 引言

随着数字信号处理越来越广泛的应用,数字锁相环DPLL(Digital Phase Lock Loop)在现代集成电路设计中也越来越普遍,特别是在数字信号处理器DSP和微处理器这类高性能数字电路应用中,数字锁相环更是一种必不可少的电路。与传统的模拟锁相环(Analog Phase-Locked Loop)相比,由于数字锁相环较少采用高阻值电阻、电容以及电感等非线性器件,可以采用与高速数字逻辑电路相兼容的制造工艺来设计和制造,也更加容易在数字系统中应用。

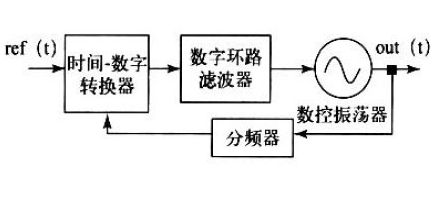

一个典型的数字锁相环结构如图1所示,数控振荡器DCO(Digital-Controlled Oscillator)是其中最关键和核心的部分。数控振荡器DCO输出了可变频率的振荡波形,决定了整个锁相环的噪声性能和功耗。数字时间转换器(Time - to - DigitalConverter)输出了参考时钟和反馈来的输出时钟之间的相位差,一个数字环形滤波器(Digital LoopFilter)代替了模拟环形滤波器来控制DCO,由与参考时钟的相位差来控制DCO输出或高或低的振荡频率,输出振荡信号由负反馈送到数字时间转换器,使相位差减小,最终让输出信号频率与参考时钟频率一致,即达到相位锁定。整个DCO 因此不再需要含有电容或电感,同时也减少漏电流和电源噪音的问题。

图1 数字锁相环的基本结构

2 电路结构和原理

数控振荡器有多种实现结构,本文设计了一种完全采用静态CMOS 逻辑电路的DCO结构,该DCO基于由CMOS 反相器构成的环形振荡器,其电路结构如图2 所示。

图2 电路结构图

如图2 所示,每一级环形振荡器均是5 个CMOS反相器串联,并构成闭环负反馈回路,每个反相器的输出也与下一级环形振荡器对应的反相器输出相连。根据巴克豪森准则:振荡器要产生振荡,那么环路增益必须大于等于一且总相移有360°。因此环路中进行反相的次数必须是奇数,三个以上的奇数个CMOS 反相器串联闭环回路,在一个微小的激励下都能够产生振荡。单级环形振荡器的振荡频率由反相器个数和其本征延迟决定,用n 表示反相器个数,tr 表示反相器上升沿延迟,tf 表示反相器下降沿延迟,频率可以用下式表示为: