今天小编要和大家分享的是接口,总线,驱动相关信息,接下来我将从USB 3.0一致性测试的方法解析,dr9公头 插座 rs232接口 串口 90度弯脚 插板式这几个方面来介绍。

接口,总线,驱动相关技术文章USB 3.0一致性测试的方法解析

虽然已经有早期的USB3.0产品上市,但向超速(SuperSpeed)USB的大规模转换还没有开始。部分问题是USB 2.0已经十分普及,生产成本非常低。高带宽设备(如视频摄像机和存储设备)成为了SuperSpeed USB的第一批应用对象。然而,至少目前为止,成本因素将USB 3.0实现仍限制用于较高端的产品。

除了广泛部署任何 新的行业标准所面临的固有挑战外,USB 3.0不仅仅是USB 2.0的常规升级,因为USB 3.0可以提供10倍的性能提升。虽然性能提高了,但消费者对低成本互连的期望一直没有改变。这就给工程师带来了巨大的压力,他们只能使用速度低得多的通道,同时仍要在各种条件下确保可靠性、互操作性和高性能。确保物理层(PHY)一致性的测试和认证从未有现在这么关键或重要。

USB 3.0共享许多其它高速串行技术(如PCI Express和串行ATA)的特性:8b/10b编码、显著的通道衰减以及扩展频谱时钟。本文将讨论一致性测试方法,以及如何对发送端、接收端、电缆及互连实施最精确、可重复的测量。掌握这些技巧后,到SuperSpeed平台集成实验室(PIL)的旅程也许会更精彩。

高速Vs.超速

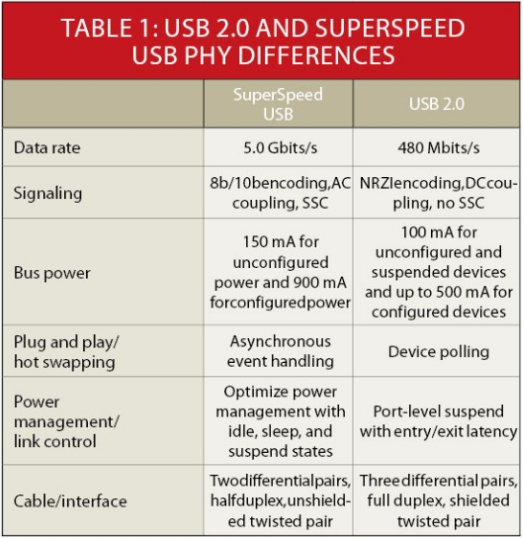

USB 3.0可以满足带宽日益增加的需求,能够支持应用提供更加实时的体验。目前在用的USB设备数量估计超过10亿,因此USB 3.0需要具有后向兼容功能,以支持传统的USB 2.0设备。当然,USB 2.0和3.0之间还有多个重要的PHY区别(表1)。

为了应对与更高速度接口有关的新挑战,SuperSpeed USB一致性测试已经作出了很大的修改。USB 2.0接收端的验证包括接收端灵敏度测试。USB 2.0设备必须响应150mV或150mV以上的测试包,同时忽略(抑制)低于100mV的信号。

另一方面,SuperSpeed USB接收端必须在有许多信号损伤的条件下还能正常工作,因此测试要求比USB 2.0更加严格。设计师还必须考虑传输线效应,并且使用包括在发送端进行去加重、在接收端进行连续时间线性均衡(CTLE)在内的均衡技术。如今还要求在接收侧进行抖动容限测试,但使用扩频时钟(SSC)和异步参考时钟可能导致互操作性问题。