今天小编要和大家分享的是接口,总线,驱动相关信息,接下来我将从基于FPGA的ARM并行总线和端口设计,netgear prosafe gs108t 8端口千兆智能交换机10/100 / 1000mbps这几个方面来介绍。

接口,总线,驱动相关技术文章基于FPGA的ARM并行总线和端口设计

通过EP2C20Q240器件和LPC2478处理器,研究ARM应用系统外部并行总线的工作原理和时序特性,以及在FPGA中进行双向总线设计的原则,设计并实现了FPGA并行总线.借助Quartus II仿真工具,对FPGA并行总线进行了时序仿真,并用SignalTap II逻辑分析仪进行在线测试,验证设计的正确性.

0 引言

在数字系统的设计中,FPGA+ARM 的系统架构得到了越来越广泛的应用,FPGA主要实现高速数据的处理;ARM 主要实现系统的流程控制.人机交互.外部通信以及FPGA 控制等功能.I2C.SPI 等串行总线接口只能实现FPGA 和ARM 之间的低速通信 ;当传输的数据量较大.要求高速传输时,就需要用并行总线来进行两者之间的高速数据传输.

下面基于ARM处理器LPC2478以及FPGA器件EP2C20Q240,以ARM外部总线的读操作时序为例,研究两者之间高速传输的并行总线;其中,数据总线为32 位;并在FPGA 内部构造了1024x32bits 的SRAM 高速存储缓冲器,以便于ARM 处理器快速读写FPGA 内部数据.

1 ARM并行总线的工作原理

ARM 处理器LPC2478 的外部并行总线由24 根地址总线.32根数据总线和若干读写.片选等控制信号线组成.根据系统需求,数据总线宽度还可以配置为8 位.16 位和32 位等几种工作模式.

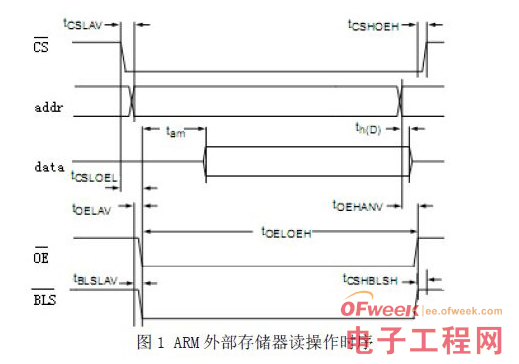

在本设计中,用到ARM 外部总线的信号有:CS.WE.OE.DATA[310].ADDR[230].BLS 等.CS 为片选信号,WE 为写使能信号,OE 为读使能信号,DATA 为数据总线,ADDR 地址总线,BLS 为字节组选择信号.ARM 的外部总线读操作时序图,分别如图1 所示.

根据ARM 外部并行总线操作的时序,ARM 外部总线的读写操作均在CS 为低电平有效的情况下进行.由于读操作和写操作不可能同时进行,因此WE 和OE 信号不能同时出现低电平的情况.

数据总线DATA 是双向的总线,要求FPGA 也要实现双向数据的传输.在时序图中给出了时序之间的制约关系,设计FPGA 时应该满足ARM 信号的建立时间和保持时间的要求,否则可能出现读写不稳定的情况.