今天小编要和大家分享的是处理器,DSP相关信息,接下来我将从基于FPGA+DSP结构实现二次雷达处理机的设计,dsp arm fpga开发板这几个方面来介绍。

处理器,DSP相关技术文章基于FPGA+DSP结构实现二次雷达处理机的设计

二次雷达(Secondary Surveillance Radar,SSR)目标识别系统能够通过发射特定的射频脉冲序列对装有应答机的目标进行“一问一答”式的询问,由应答机的应答脉冲码获得目标的高度、编号等信息。航管二次雷达常用的基本工作模式为传统的A/C模式和新近的S模式。

A模式提供飞机的代码,C模式提供飞机的高度码。但是,传统的A/C 模式存在一些技术缺陷,如多目标代码交织、重叠、多径反射,同步窜扰,异步干扰等。这在大型航空港等飞机非常密集的地方,时间不同步和混淆信号已经越来越严重,同时单脉冲二次雷达无法提供数据链路的服务。

针对上述情况出现了一种新式的二次雷达--S模式二次雷达。S模式是一种先进的雷达询问系统,它建立在独立编址和选择性询问的基础上,能够解决在模式A/C中具有的信号干扰、有限的信息编码、幻影(garble)和异步应答(fruit)等问题,同时在数据链路方面也具有巨大的潜力。

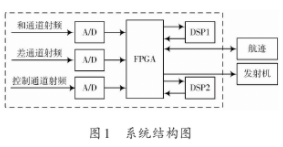

本文采用通行的FPGA+DSP 结构,结构简单清晰,功能强大,成本相对较低,实现了3/A、C、二级S模式码发射;接收并处理三路射频信号,检测并正确提取AC码、S码及相应参数,;输出航管的A模式,C模式和S模式编码信号,并有较强的抗干扰能力。

1 二次雷达处理机基本性能要求

二次雷达指标为:工作模式3/A、二级S模式功能,处理能力≥10 000 点/帧,同时≥900 批/帧。抗异步串扰密度10 000 fruits/s;检测概率≥99%,虚警率1个/帧,解码有效率≥99%;具有接收旁瓣抑制和询问旁瓣抑制能力,可自适应反串扰和他站应答干扰;具有抑制反射假目标的能力。

根据上面基本要求,二次雷达可以按任务分解为:

解码、发射时序、点迹处理、通信四种功能。相对而言,FPGA易于处理大数据量的流水数据,不适于复杂算法的事务处理,开发调试困难。DSP功能强大、运算速度快、寻址灵活、通信能力强,易于开发;但有些功能仅DSP 无法完成,必须有FPGA 配合。这就要在FPGA 和DSP 之间合理分配任务。因此这里除了点迹由DSP 处理外,其他都由FPGA来完成。系统结构如图1所示。