今天小编要和大家分享的是工艺,制造相关信息,接下来我将从原子级工艺实现纳米级图形结构的要求,intel已开始研发7nm,5nm工艺这几个方面来介绍。

工艺,制造相关技术文章原子级工艺实现纳米级图形结构的要求

原子层刻蚀和沉积工艺利用自限性反应,提供原子级控制。泛林集团先进技术发展事业部公司副总裁潘阳博士分享了他对这个话题的看法。

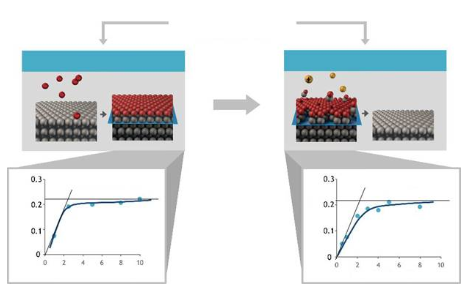

图 1. 原子层工艺中的所有半周期反应是自限性反应。

技术节点的每次进步都要求对制造工艺变化进行更严格的控制。最先进的工艺现在可以达到仅7 nm的fin宽度,比30个硅原子稍大一点。半导体制造已经跨越了从纳米级到原子级工艺的门槛。工程师现在必须关注结构的尺寸变化,仅相当于几个原子大小。由于多重图案模式等复杂集成增加了工艺数量,进一步限制了每个步骤允许的变化。3D NAND和finFET结构的复杂性会带来更高挑战。

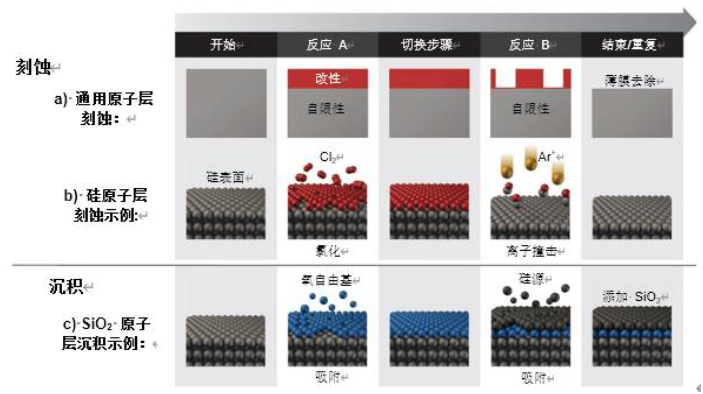

图 2. 原子层工艺能够去除或沉积材料。在以上刻蚀示例中,氯吸附到硅表面,然后通过氩离子撞击去除改性层。在沉积示例中,氧吸附到硅表面,硅与改性表面层相结合,沉积二氧化硅。

对于半导体行业而言,控制工艺变化始终都是一大关键挑战,因为它会直接影响到产品的性能、良率和可靠性,进而产生重大经济后果。工艺诱生的变化有多个来源,包括晶粒、晶圆和工具。要控制这些变化,一种方式是通过运用原子层沉积 (ALD) 和原子层刻蚀 (ALE) 等技术,这些技术本身比传统等离子体方法更加精确。

原子层工艺

原子层工艺包括沉积和刻蚀解决方案,它们具有一些共同的特征。与连续工艺不同,它们分周期进行,每个周期都会添加或去除有限固定数量的分子层。每个周期又分为若干半周期,每个半周期分别是不同的自限性工艺,为下个半周期准备表面。例如,在 SiO2 沉积中(图1和2),第一个半周期会吸附氧原子,这个过程是自限性的,受到结合位点的限制。然后,多余的氧被从腔室中清除,表面暴露在硅原子源下,硅原子与吸附的氧发生反应,形成一层 SiO2。这个半周期工艺也是自限性的,在这种情况下,它受到氧的限制。原子层沉积的自限和有序的特性在先进逻辑和存储器芯片HVM中得到了广泛应用。