今天小编要和大家分享的是EDA,IC设计相关信息,接下来我将从veriloghdl的关键字_Verilog HDL的程序结构,verilog5视频这几个方面来介绍。

EDA,IC设计相关技术文章veriloghdl的关键字_Verilog HDL的程序结构

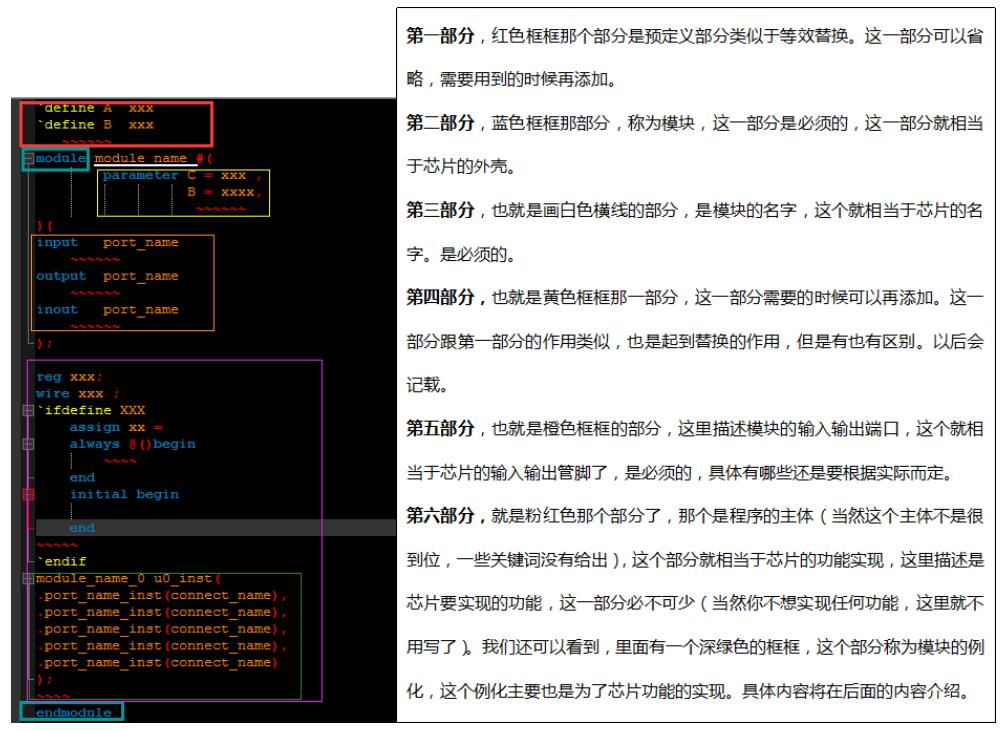

Verilog HDL的程序结构

首先我们不开始讲Verilog HDL的语法,我们从Verilog HDL的程序结构出发。相信大家都看过芯片吧,它有个名字,有个外壳,外壳向外伸出有引脚(BGA封装的那种请不要乱搅和),然后芯片它可以实现一定的功能。

Ok,知道这些之后,我们就来看看Verilog HDL的描述数字电路的程序结构吧。

在解释结构的时候,我拿芯片设计这个例子来打一个不恰当的比方。

VerilogHDL程序的大致结构就是这么一个形式,每一个模块的结构都是一致的只不过语句之间存在一些差别,每一部分的具体描述将在后面进行。

二、verilog程序结构的简单描述

OK,现在让我们现在开始了解一下一些语法和注意事项(注意,我这里不会把语法讲得很细很细,我主要是描述一些(我,或者初学者)易忘的,关键的语法和知识点),描述的顺序不一定按照上面的各个部分哟,我们先描述一些VerilogHDL程序必须的。

首先是模块说明:

module 和 endmodule ,这两个关键词成对出现,一般的内容都会囊括在这两个两个关键词之间。一个verilog(.v)文件可以有多个module 。。.endmodule,但是为了方便管理,建议只实现一个。

此外无论是能够综合成电路的verilog程序还是只是仿真的程序,都需要以模块的形式给出。

模块名:

①模块名的定义要符合标识符的定义,至于什么是标识符,以后会说的。此外也要注意书写的规范性。

端口说明:

①端口可以比方成芯片的输入输入管脚,它只有三种类型:输入,输出,双向;

②端口有一些附加属性,如数据类型、符号特性、位宽等;input端口只能是线网类型,output可以是寄存器类型也可以是线网类型,inout也只能是线网类型。至于线网类型和寄存器类型,在以后的数据类型中会介绍。

③当端口是总线类型时,可以简单地理解为端口有多位时,对应于同时描述芯片的多个管脚时,可以给端口加上位宽。即input wire [M:N] a;如果M》N,则为降序,a[M]为最高位,位宽为M-N+1位;如果M《N,则最高位位a[N]位,位宽位N-M+1位;