今天小编要和大家分享的是模拟技术相关信息,接下来我将从三种不同的ADC驱动器架构和应用分析,进口原装集成电路国半模拟转换器 adc0809ccn adc这几个方面来介绍。

模拟技术相关技术文章三种不同的ADC驱动器架构和应用分析

一般而言,用来驱动现今高分辨率类比/数码转换器的电源都是拥有数百欧姆或以上的AC或DC负载。因此,一个具备有高输入阻抗(数百万欧姆)和低输出阻抗的运算放大器便成为ADC驱动器输入的最佳选择。ADC驱动器可作为缓冲器和低通滤波器之应用,以减低系统的整体杂讯。

随着讯号在电路板的布线和冗长电缆上传送,系统杂讯会积聚在讯号里,而一个差动ADC会拒绝任何看来像共模电压的讯号杂讯。相比起单端的讯号,采用差动讯号有好几个优点。首先,差动讯号可将ADC的动态范围增大一倍。其次,它可提供更佳的谐波失真效能。现今有几个方法可从一个双重运算放大器配置产生出差动讯号。其中一种方法是采用单端/差动转换技术,而另一种则需动用差动输入源。为了利用完全的ADC的动态范围,ADC的输入必须被驱动至满刻度的输入电压。

本文将会讨论三种不同的ADC驱动器架构:单到单、单端到差动和差动到差动。主要目的是希望能扼要地提供一切用ADC介接高效能运算放大器的资料。

讯号路径的必要组件

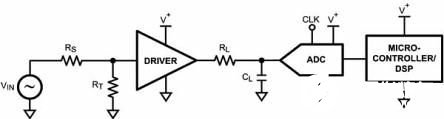

以下会把讯号路径中的类比前端设计之几个组成部份一起讨论。典型讯号路径的类比前端包括有一个用来驱动ADC的运算放大器、一个RC滤波器、ADC和微控制器或数码讯号处理器(DSP)。

图1:典型讯号路径的类比前端方块图

现实世界中的输入源会带有不理想的阻抗,因此需依赖一个很低输出阻抗的缓冲放大器来驱动ADC的输入。然而,外置的RL-CL滤波器会作用为一个抗叠频滤波器,以帮助减低ADC驱动器的杂讯频宽,以及缓冲由ADC取样和保持电路所引致的充电瞬时。为了尽量减低输入电压的跌降,外置的并列电容(CL)必须比ADC的内置输入电容大10倍,而同时外置的串行电容(RL)亦必须够大以固定发生在运算放大器输出的相位延迟,从而维持电路的稳定性。对于大部份的应用而言,在运算放大器输出和ADC输入之间用一个串行隔离电阻来连接,都可以带来益处,因为这个串行电阻可有助限制运算放大器的输出电流,而为这个串行电阻选定数值是一项非常重要的工作。