今天小编要和大家分享的是存储技术相关信息,接下来我将从利用多端口存储器双口RAM和FIFO实现多机系统的设计,fpga image processing program (two) --fifo fft ram这几个方面来介绍。

存储技术相关技术文章利用多端口存储器双口RAM和FIFO实现多机系统的设计

前言

在测控、仪器仪表、语音信号处理和图像通信领域中往往需要多处理器分工完成数字信号处理(DSP)算法和与外部系统的通信、控制、数据采集和人机接口功能。在多机系统中,CPU之间的通信常采用以下几种方式:(1)串行通信。这种方式相对简单,由于受到波特率的限制,在不同档次单片机之间需要通信业务大的场合得不到很好的通信效果。(2)并行通信。利用CPU的I/O功能在CPU之间增加缓冲器或锁存器实现双机通信。通信性能较串行通信有所提高,但仍然得不到理想的效果。(3)利用共享式存储器实现。DMA方式就是其中的一种,能够达到数据的高速传输,但不能同时访问存储器,CPU必须等待总线,而且有些CPU不支持DMA功能。另一种是利用多端口存储器,双口RAM和FIFO是常用的两种多端口的存储器,允许多CPU同时访问存储器,大大提高了通信效率,而且对CPU没有过多的要求,特别适合异种CPU之间异步高速系统中。因此,受到硬件设计者的青睐。

一、两种多端口存储器

1.双口RAM的仲裁控制

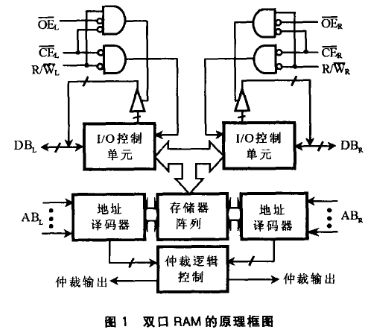

双口RAM是常见的共享式多端口存储器,以图1所示通用双口静态RAM为例来说明双口RAM的工作原理和仲裁逻辑控制。双口RAM最大的特点是存储数据共享。图1中,一个存储器配备两套独立的地址、数据和控制线,允许两个独立的CPU或控制器同时异步地访问存储单元。既然数据共享,就必须存在访问仲裁控制。内部仲裁逻辑控制提供以下功能:对同一地址单元访问的时序控制;存储单元数据块的访问权限分配;信令交换逻辑(例如中断信号)等。

(1)对同一地址单元访问的竞争控制

如果同时访问双口RAM的同一存储单元,势必造成数据访问失真。为了防止冲突的发生,采用Busy逻辑控制,也称硬件地址仲裁逻辑。图2给出了地址总线发生匹配时的竞争时序。,此处只给出了地址总线选通信信号先于片选脉冲信号的情况,而且,两端的片选信号至少相差tAPS――仲裁最小时间间隔(IDT7132为5ns),内部仲裁逻辑控制才可给后访问的一方输出Busy闭锁信号,将访问权交给另一方直至结束对该地址单元的访问,才撤消Busy闭锁信号,将访问权交给另一方直至结束对该地址单元的访问,才撤消Busy闭锁信号。即使在极限情况,两个CPU几乎同时访问同一单元――地址匹配时片选信号低跳变之差少于tAPS,Busy闭锁信号也仅输出给其中任一CPU,只允许一个CPU访问该地址单元。仲裁控制不会同时向两个CPU发Busy闭锁信号。