今天小编要和大家分享的是可编程逻辑相关信息,接下来我将从借助存储器的工作原理及在跨时钟域通信中的使用,fpga image processing program (two) --fifo fft ram这几个方面来介绍。

可编程逻辑相关技术文章借助存储器的工作原理及在跨时钟域通信中的使用

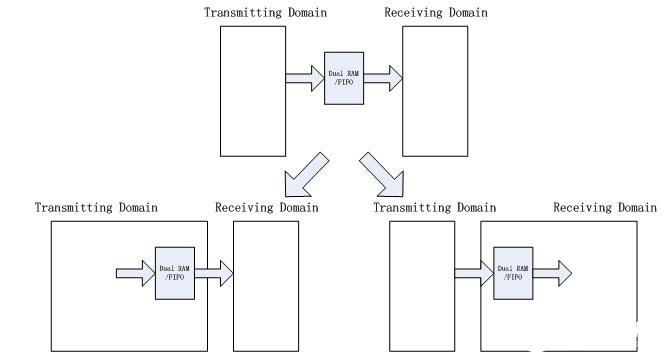

为了达到可靠的数据传输,借助存储器来完成跨时钟域通信也是很常用的手段。在早期的跨时钟域设计中,在两个处理器间添加一个双口RAM或者FIFO来完成相互间的数据交换是很常见的做法。如今的FPGA大都集成了一些用户可灵活配置的存储块,因此,使用开发商提供的免费IP核可以很方便的嵌入一些常用的存储器来完成跨时钟域数据传输的任务。使用内嵌存储器和使用外部扩展存储器的基本原理是一样的,如图1所示。

图1 借助存储器的跨时钟域传输

双口RAM更适合于需要互通信的设计,只要双方对地址做好适当的分配,那么剩下的工作只是控制好存储器的读写时序。FIFO本身的特性(先进先出)决定了它更适合于单向的数据传输。总之,借助存储器进行跨时钟域传输的最大好处在于,设计者不需要再花时间和精力考虑如何处理同步问题,因为这些工作都交给了存储器,我们也不用关心存储器内部到底使用了怎样的工作机制来解决冲突问题(当然了,存储芯片内部肯定是有一套完善的同步处理机制)。我们可以把更多的时间花在数据流以及存储器接口的控制上。借助存储器的另一个优势,它可以大大提高通信双方的数据吞吐率,它不像握手信号和逻辑同步处理机制那样在同步设计上耗费太多的时钟周期,它的速度瓶颈基本就是存储器本身的速度上限。不过,在得到便利的同时,我们也不得不以付出更多的Money作为代价。

下文将重点探讨异步FIFO在跨时钟域通信中的使用。常见的异步FIFO接口如图2所示,FIFO两侧会有相对独立的两套控制总线。若写入请求wrreq在写入时钟wrclk的上升沿处于有效状态,那么FIFO将在该时钟沿将锁存写入数据总线wrdata。同理,若读请求rdreq在读时钟rdclk的上升沿处于有效状态,那么FIFO将把数据放置到读数据总线rddata上,外部逻辑一般在下一个有效时钟沿读取该数据。