今天小编要和大家分享的是可编程逻辑相关信息,接下来我将从一种基于FPGA内部存储器的适合音频解嵌的高效异步FIFO设计,异步fifoppt这几个方面来介绍。

可编程逻辑相关技术文章一种基于FPGA内部存储器的适合音频解嵌的高效异步FIFO设计

在视音频嵌入解嵌系统中,嵌入音频、音频解嵌与音频转换成音频帧标准格式输出都是工作在不同的时钟频率下的。多时钟带来的问题就是如何设计异步时钟之间的接口电路。

异步FIFO存储器是一种在数据交互系统中得到广泛应用的先进先出逻辑器件,具有容纳异步信号的频率(或相位差异)的特点。使用异步FIFO可以在两个不同时钟系统之间快速而方便地传输实时数据。因此,异步FIFO被广泛应用于实时数据传输、网络接口、图像处理等方面。

虽然目前也出现了一些通用的异步FIFO内核,但在一些具体环境下其工作效率并不是最理想的。针对这个问题,本文介绍了一种适合音频解嵌的高效异步FIFO,对通用异步FIFO进行了一些改进,最后利用Verilog HDL硬件描述语言设计并仿真实现。

1 SDI音频嵌入基本格式

在模拟视频中存在着行、场消隐期,而行、场消隐期内并不存在有效图像信号。对于数字视频信号,同样地也存在没有有效视频信号的区间。

模拟视频中的行消隐期间,在数字视频中被称为行辅助数据区HANC(Horizontal Ancillary Data)。分量数字视频格式的每一个有效行中,625/50制共有1 728个取样字(525/60制为1 716个取样字),其中对Y、Cb和Cr取样有1 440个取样字(0~1 439)。而对行消隐期间的取样可以有288个取样字(525/60制为276个取样字)。

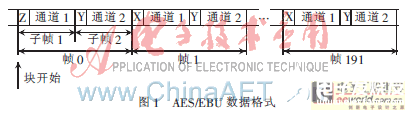

目前辅助数据区也即行消隐区最大的用途是放置数字音频,被放置的数字音频称为嵌入音频。图1是AES/EBU音频数据块结构[1]。

一个音频块由192个连续帧组成,每个帧包含相关的两个子帧,使得一个数字音频码流可以作为立体声、双声道模式使用。这两个子帧(32 bit)分别表示一个音频通道中的一个音频样本,每个子帧的32 bit中包含24 bit的音频数据和一些辅助数据。

音频嵌入就是将每个子帧的32 bit信息按照SMPTE-292[2]标准分别嵌入到3个数据字和一个辅助数据字中,并将这些数据字嵌入到HANC中。解嵌的目的就是把每个音频子帧对应的这4个字找到,按照顺序把这些子帧组合成AES/EBU音频块格式,使输出为直接可识别的音频码流。